Other Parts Discussed in Thread: LMH3401EVM, ADC12DJ2700EVM, LMH5401EVM, LMH3401, LMK04828, LMX2582

主题中讨论的其他器件: LMH5401EVM、LMH3401EVM 、 LMH3401、 LMK04828、 LMX2582

大家好!

我们遇到了 在更改直流输入电平后 ADC 样本达到稳定基线的问题。

在进行详细说明之后:

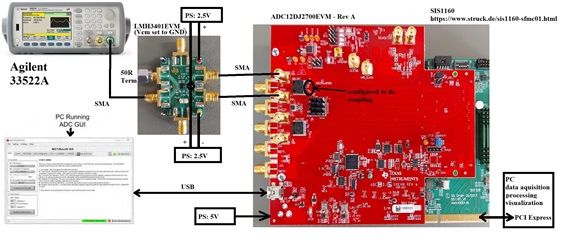

硬件:

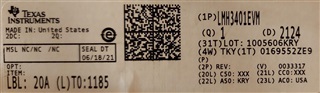

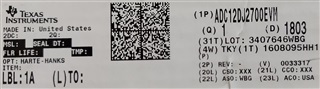

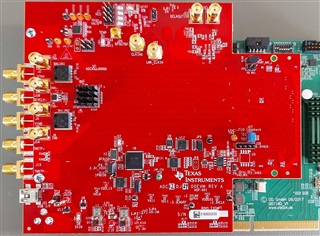

-评估板 ADC12DJ2700EVM

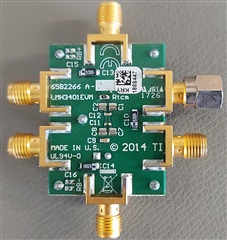

-评估板 LMH5401EVM (CM 输入连接至 GND)

- AWG 方波50秒高, 50秒低(水平与样本数据中所见)

使用"ADC12DJxx00 GUI"的设置:

-评估板 LMH5401EVM SMA IN+从 AWG 方波驱动(直流耦合)、SMA IN-端接50欧姆

- LMH5401EVM SMA OUT +/-连接至 ADC12DJ2700EVM SMA INA+/-(通道 A 直流耦合)

- ADC 时钟2.5 GHz(板载生成)

- ADC 模拟输入范围默认值

- JMode 0 (单通道5GSPS)

- ADC 数据格式偏移二进制(数据十进制数2048对应于差分输入电平0V)

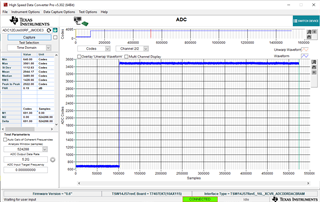

-一次性设置 ADC 并开始,连续自由运行采样

-在一定的延迟后从 ADC 数据流中获取样本

数据处理:

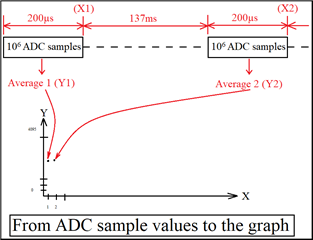

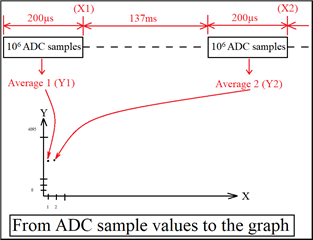

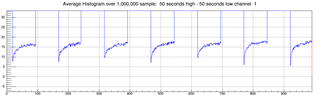

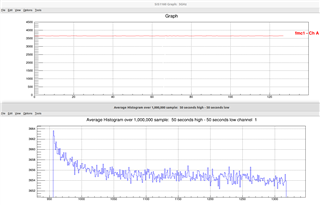

-图中沿 x 轴的每个点对应于100万个样本的平均值(0.2毫秒迹线)

-每137ms 一个数据点

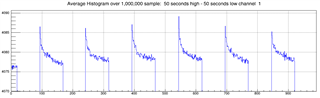

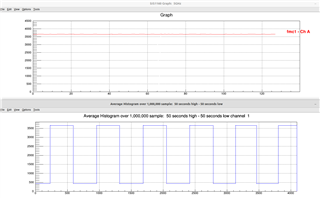

- AWG 水平调整为 ADC 数据约十进制3655 (高电平)和445 (低电平)

-见图片 screen4.png

可以观察到的情况:

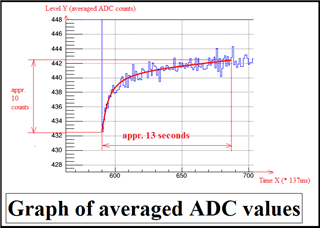

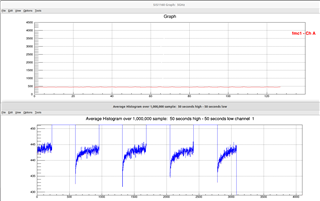

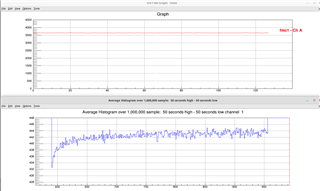

-在信号边沿(上升或下降),"平均数据点"显示过冲

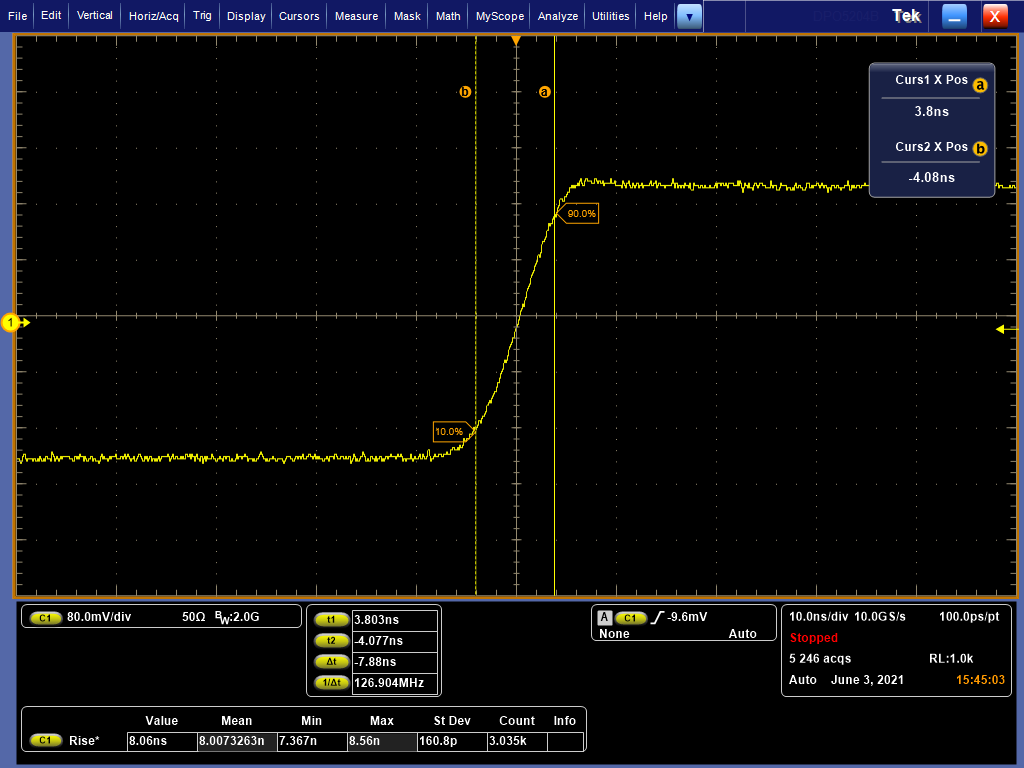

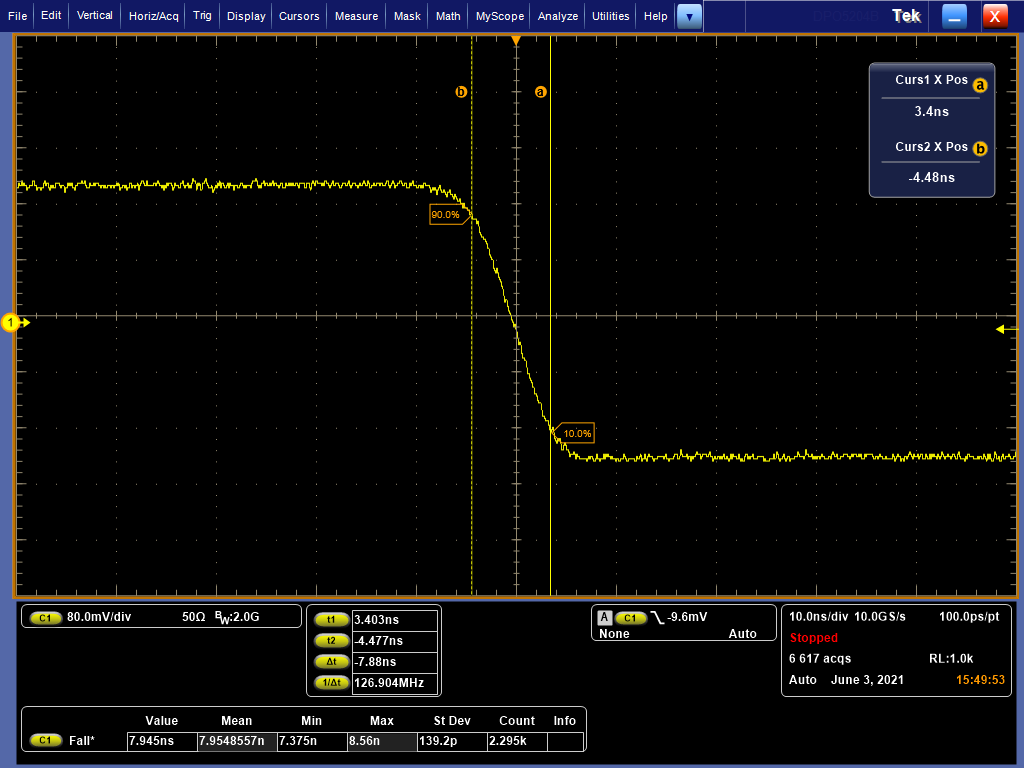

-见图片 screen2.png 和 screen3.png

-像电容器充电或放电曲线,"平均数据点"需要一段时间(~1分钟?) 以达到稳定值(基准值)

-放大过冲区域,见图片 screen5.png 和 screen6.png

您能否确认此行为?

这可以改进或避免吗?

此致

Andreas