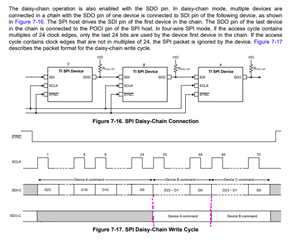

您好、我们有一个硬件板、其中包含8个菊花链 DAC63204器件、这些器件的接线方式如随附图片所示。 每个 SDO 引脚通过一个1k 上拉电阻器连接到 VCC、并以菊花链方式连接到 SDI 线路中的第二个器件。

时钟速度为500kHz 和 SPI 模式1。

首先、我们将 SDO_EN 位设置为1、然后我们将寄存器配置为在器件的通道3上输出3.3V。 我们试图通过编程每个单独的设备和设备响应根据固件.

在菊花链模式下、器件绝不会在时钟沿记录数据通过线路中的第一个器件。 是否有任何其他特定要求才能使菊花链模式正常工作?

请注意:数据表中规定 SDO 引脚需要一个上拉电阻器、而 SDI 需要保持悬空、基本而言、在菊花链模式下这是不可能的。

数据表在布局部分中的标签也不正确、如下所示: