主题中讨论的其他器件:, LMK04826.

您好!

我尝试使用 JESD 接口和 TI204 IP 运行 ADS52J90。 我知道 TI204 IP 产生与 I 和 Q 相关的输出值,因此它始终会看到一对 ADC 通道彼此相关。 但我只需要分离正常 ADC 值、我如何才能实现它?

此致!

曼努埃尔

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好!

我尝试使用 JESD 接口和 TI204 IP 运行 ADS52J90。 我知道 TI204 IP 产生与 I 和 Q 相关的输出值,因此它始终会看到一对 ADC 通道彼此相关。 但我只需要分离正常 ADC 值、我如何才能实现它?

此致!

曼努埃尔

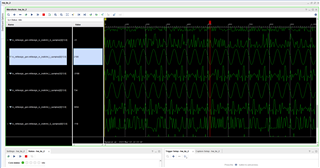

问题是、当我仅将 ADC 的 ADS52J90EVM 板的 ch9连接到2MHz sinus 信号时、我要在 Xilinx ILA 中测量正确的 sinus 信号(请参阅图示)

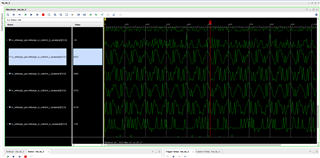

但是、如果我将另一个2MHz 信号连接到 EVM 的 CH11、我将得到以下结果

如您所见、我不再具有正确的窦性、但在四个通道上仍然有一些高电平信号。 它似乎以某种方式相关、这就是我认为它可能是某种集成到 IP 或 ADC 中的 IQ 转换的原因。

现在、问题是这个问题是来自您的 IP 还是 ADC? 或者它可以是其他东西吗?

您好、Manuel:

您能否分享更多有关您的设置的信息? 下面是几个问题:

1.速度是多少? 您是否使用16通道模式?

2. num_adc_per_lane =? (它相当于40x、80x 和160x 的串行化)

3.您使用的是 DEMOD 吗? 如果是、抽取因子、压缩因子等设置是什么?

4.您能否尝试使用设备的内部测试模式进行数据采集,看看捕获的数据是否合理。

5.您的 ILA 中与 CH4_I_SAMPLES [0]等类似的不同数据行是什么?

在我看来、我认为这个问题可能与器件的配置有关。

谢谢。此致、

Abhishek

你好,Abhishek

您可以在下面找到您问题的答案编号。

1.进一步了解

ADC 参数:

速度= 1.562Gbps

FPGA GTX 时钟= 156.25MHz

FPGA/ADC SysREF = 4.8828125MHz

ADC 时钟= 39.0625MHz

FPGA 时钟= 156.25MHz

模式= 16通道模式

JESD 参数:

L = 8

M = 16

S = 1

f = 4

2.每通道 ADC 数= 2

3.解调:

我不会使用 Demod 节点、但我不知道哪个寄存器属于它。 因此、它可能已打开、但我不想使用它!

您能否向我发送 DEMOD 寄存器、因为在数据表中这些寄存器缺失。

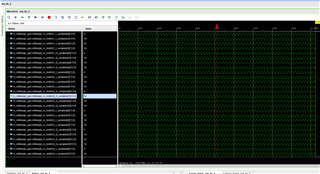

4.测试模式

我使用了斜坡测试模式、对于所有通道而言、这种模式看起来都正常:

5.配置:

CML_1 = ADC1和 ADC2

CML_2 = ADC3和 ADC4

CML_3 = ADC5和 ADC6

CML_4 = ADC7和 ADC8

CML_5 = ADC9和 ADC10

CML_6 = ADC11和 ADC12

CML_7 = ADC13和 ADC14

CML_8 = ADC15和 ADC16

在中用 ILA 测量:

ADC1 = CH3_I_SAMPLES [0]和 CH3_I_SAMPLES [2]

ADC1 = CH3_I_SAMPLES [0]和 CH3_I_SAMPLES [2]

ADC1 = CH3_I_SAMPLES [0]和 CH3_I_SAMPLES [2]

ADC1 = CH3_I_SAMPLES [0]和 CH3_I_SAMPLES [2]

ADC1 = CH3_I_SAMPLES [0]和 CH3_I_SAMPLES [2]

ADC1 = CH3_I_SAMPLES [0]和 CH3_I_SAMPLES [2]

ADC1 = CH3_I_SAMPLES [0]和 CH3_I_SAMPLES [2]

最后、这里是 ADS52J92 EVB 配置文件:

您好、Manuel:

很抱歉、由于紧急情况、我不能入住。

我看了看你们分享的数据。 我对您分享的数据有一些疑问:

1. 1.进一步了解

ADC 参数:

速度= 1.562Gbps = 39.0625 x 16位 x 2通道 x 10位/8位 = FS x 40 (40倍串行化);设备执行40倍 串行化

FPGA GTX 时钟= 156.25MHz (为什么设置此频率?) FPGA 中的反串行化是否以10倍的速度发生?

FPGA/ADC SysREF = 4.8828125MHz -请检查这是否确实是正确的频率。

ADC 时钟= 39.0625MHz

FPGA 时钟= 156.25MHz -请检查此项

模式= 16通道模式

我认为您应该首先检查您的时钟方案。 从您共享的配置文件中、我想您正在时钟分频器模式下使用 LMK04826、其中的分频因数为1表示 FPGA_GTX clock、4表示 ADC_clk、1表示 FPGA_clk。 但是、在原始配置文件中、我认为它有所不同。 即 1表示 FPGA_GTX 时钟、2表示 ADC_clk、4表示 FPGA_clk

接下来

3. DEMOD:要禁用 DEMOD、请写入 Reg3[0]- EN_DEMOD = 0;我可以向您共享 DEMOD 寄存器映射。 请在 abhishek.vishwa27@ti.com 上单独给我发送一封关于同一主题的电子邮件

4.斜坡模式:斜坡模式看起来不正确,它始终是向上斜坡,当它达到全值时,它重置并重新开始。 此外、我认为它不是14位斜坡模式、因为它的重复性非常快。

顺便说一下、您是使用客户的 EVM & TSW14J56采集解决方案、还是使用另一个 FPGA 构建您自己的采集解决方案?

如果您使用的是客户 EVM、您能否共享时钟连接、此外、如果可能、您能否使用示波器查看时钟输出并检查它们是否正确。

谢谢。此致、

Abhishek

Hy Abhishek,

非常感谢您的回答。

1.对于我尝试的参数、尽量与您提供的示例设计接近。 40倍串行化是芯片的一个问题、还是我必须考虑这一点?

FPGA GTX 时钟为156.25MHz、因为我使用与 FPGA 时钟相同的时钟。 关于选择 GTX 时钟、我需要知道什么吗? 如何最终在 FPGA 上实现10倍的反串行化?

我将回顾我的时钟方案、我只是不确定用于 GTX 时钟的频率、以及它与其他频率的关系如何。

3.我会给大家发一封关于 DEMOD 寄存器规格的邮件.

4.感谢提示。 现在我知道输出有误、我 可以再次开始使用测试图形进行验证

5.不、我不使用 TSW14J56、因为它已过时。 我正在使用 Xilinx 的 ZCU102。 我使用示波器验证了时钟输出、可能再次这样做很值得。

谢谢、此致 Manuel

您好、Manuel:

是的、您说得对、默认情况下该器件将位于子类1 JESD204B 中。 我刚才提到如果您需要更改、请确保设置 ENABLE_JESD_VER_CONTROL。 就这些。

感谢您确认您不使用 TSW。 但是、您有 ADS52J90的客户 EVM、对吗?

您能否告知哪个输入时钟将进入 LMK04826器件? 它是40MHz 振荡器、还是来自外部连接器? 由于配置文件要在时钟分频器模式下配置 LMK、我假设您必须在 SMA 连接器上提供外部时钟。 我对吗?

关于 FPGA GTX 时钟 :

正如我所解释的、由于设备以1.562Gbps 的通道速率发送数据、因此设备要做到这一点、就要以40倍的速率有效地进行串行化。 它将生成 FS x 40的时钟。 因此、在本例中、它为:39.0625 x 40 MHz = 1.562 GHz。

同样在 FPGA 端、FPGA 以1.562 Gbps 的速率接收串行数据、然后必须进行反串行化、我通常已经看到 FPGA 使用固定的40倍反串行化( 您能否确认这一点 )。 因此、到 FPGA 的 GTX 时钟应该与 ADC CLK 一样(仅当 FPGA 内部的反串行化为40倍时)。

否则、您必须相应地缩放 GTX 时钟以匹配器件端和 FPGA 端的通道速率

例如、在4通道模式下:

FS x 4通道 x 16位 x 10b/8b = FS x 80 --> 80x 串行化

假设 FPGA 反串行化因子是40倍。

然后、为了与车道匹配、您具有:

Fs x 80 = Fgtx x 40

因此、Fgtx (FPGA_GTX CLK)将= 2 x fs

希望这对您有所帮助。

谢谢。此致、

Abhishek

Hy Abhishek,

可以、对于 ADS52J90、我正在使用您的 EVM ADS52J90EVM。

我意识到我使用了错误的 SYSREF 时钟、因为它不是 LMFC 时钟的倍数。 因此、我将 SYSREF 分频器从32更改为40。 您可以在附件中找到新的配置文件。

不幸的是、对于新的 SYSREF、我也遇到了旧问题。

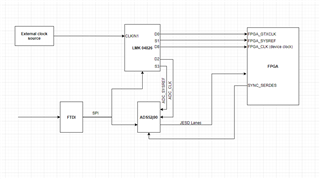

时钟连接方式如下图所示、具有156.25MHz 的外部输入时钟源:

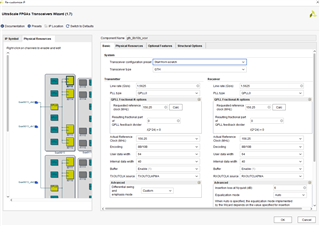

对于 FPGA GTX 时钟、我找不到任何解串化选项。 正如您接下来看到的那样、我只需要设置参考时钟和通道速率:

您好、Manuel:

下面是我收到的反馈。

"

线速率1.5625Gbps 的计算似乎准确无误。 收发器的参考时钟可以是来自下拉链路的任何频率(因为收发器中的 PLL 会将其缩放到线速率)。

如果您选择64的解串化宽度、每个时钟周期(在 Rx_sys_clock 端)将为19.53125MHz、并且 IP 将为每个 ADC 生成2个样本/周期。 如果反序列化减少到32位、您将需要修改 JESD IP 的一些参数以使其正常工作(我想我最初是为64位宽度生成它的)。

"

您能否将反串行化宽度更改为32位并检查数据是否正确传入。

谢谢。此致、

Abhishek