主题中讨论的其他器件: LMK04828

大家好!

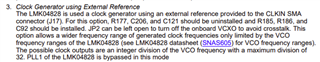

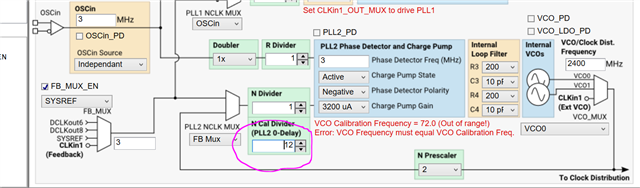

我使用 DAC37J84EVM 板、外部参考 OSCin。 我进行了用户指南(随附图片)中提到的修改。

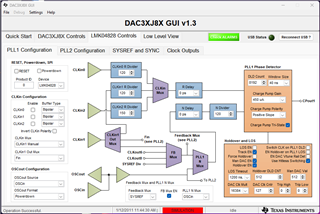

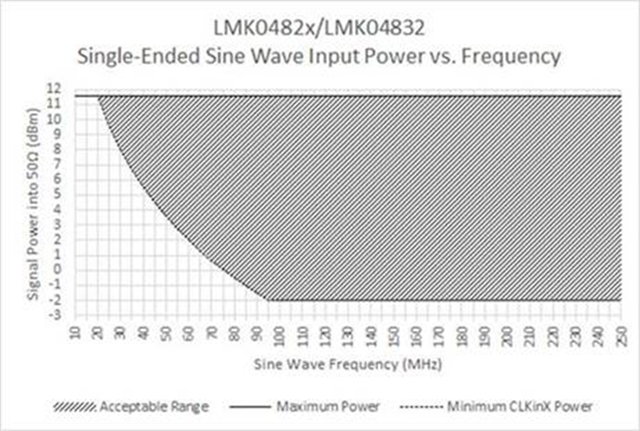

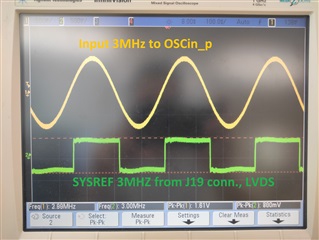

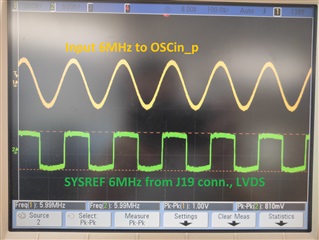

我将使用外部基准3MHz 2Vpp。

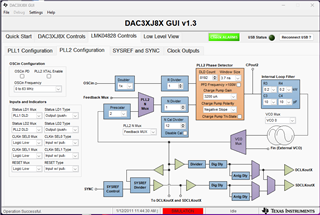

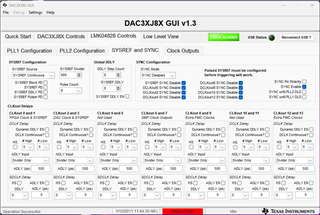

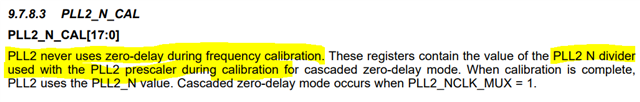

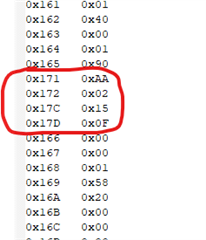

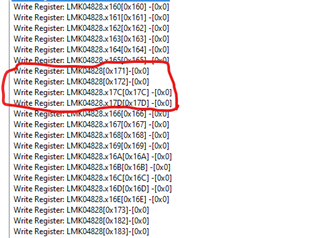

仅限 PLL2、通过反馈多路复用器提供 SYSREF 反馈的零延迟。

SYSREF 分频器= 800。 预期 VCO0频率= 3MHz * 800 = 2400MHz。

当我加载配置时、通常 PLL2不会锁定。 仅当我将 SYSREF 分频器更改为920 (有时为812)时才会锁定、但 VCO0频率变得高于数据表中提到的最大值(3MHz * 920 = 2760MHz)。

为什么不使用 SYSREF 分频器锁定= 800?

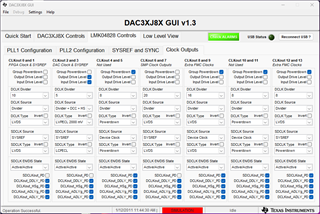

从 DAC3XJ8X GUI 附加我的配置。