下午好!

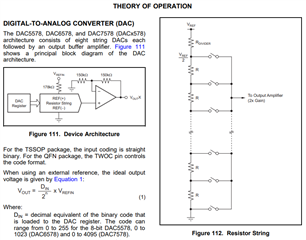

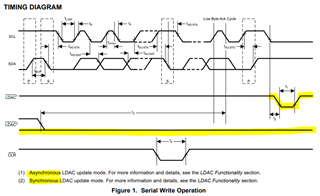

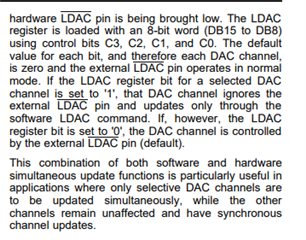

总体问题:我是否需要 将引脚1或8映射到任何内容? 我是否需要为 DAC 提供任何其他命令、以 可能地将其输入从数据缓冲器移动到寄存器? 除了向 AVDD 施加电压并将 GND 连接到适当的引脚以外、是否需要为 DAC 进一步供电?

我想知道是否还需要执行其他步骤、才能使物联网设备 DAC6578正常运行。 我将跟随 数据表 P40上的 Ex1。

接收验证了每个必要的命令都是发送到 I2C 总线、DAC 确认了这些命令(i2c SDA 在第9位位置拉低)

-我使用的是 TSSOP 封装。

-I 将3V3应用于引脚3 (AVDD)

引脚1 (LDACn)和引脚8 (Vrefin)悬空。

我的理解是、由于我将中量程写入寄存器 A (与上述示例完全相同)、并且电压范围为0至3V3、因此我将在引脚4 (Vout_A)上自动看到1.65V。 我的期望是否偏离了?

除此之外、"加载 DAC"意味着什么?