下午好!

我们正在考虑将 ADS1675用于我们的设计、但 在数据表中找不到显示时钟抖动容差与 SNR 之间关系的规格。 是否有其他资源可以显示这种相关性(图形或规格)?

感谢您的帮助!

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好 Mitchell:

欢迎加入 TI e2e 社区。

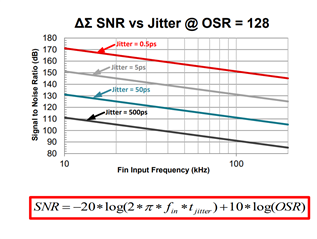

本次 TI 高精度实验室演示将讨论过采样 ADC 的抖动。

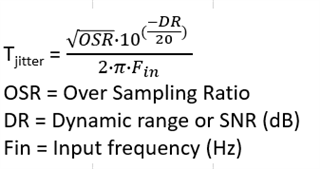

用于计算抖动的公式如下所示:

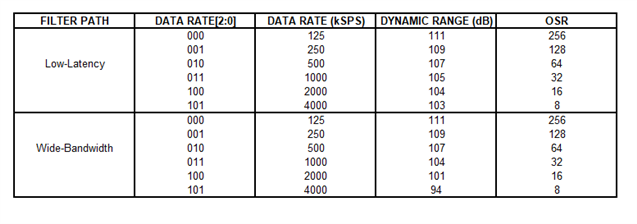

OSR 是过采样率、动态范围(DR)可用于估算 SNR。 下表突出显示了 ADS1675中的不同 OSR 选项。

fin 是将被采样的最大输入信号频率、t 抖动可使用上述公式求解。

将抖动公式中的 DR 目标设置为比 ADC 实际动态范围大20dB (对于125kSPS 示例、设置为111+20=131dB)、可以将与抖动相关的噪声降低到可以忽略不计的水平、而不会降低 ADC 噪声。 假设最大输入奈奎斯特频率为1/2*Fdata=1/2*125k=62.5kHz。

T 型抖动=(SQRT(256)*10^(-131/20))/(2*PI*62500)

T 抖动=11.5ps-rms

对于高达62500Hz 的输入频率、少于11.5ps 的时钟抖动对总噪声的影响可忽略不计。 如果系统中的最大输入频率较小、例如10kHz、则允许的最大抖动将增大。

T 型抖动=(SQRT(256)*10^(-131/20))/(2*PI*10000)

T 抖动=71.8ps-rms

如果您有其他问题、敬请告知。

此致、

Keith Nicholas

精密 ADC 应用