主题中讨论的其他器件: ADS1158

您好!

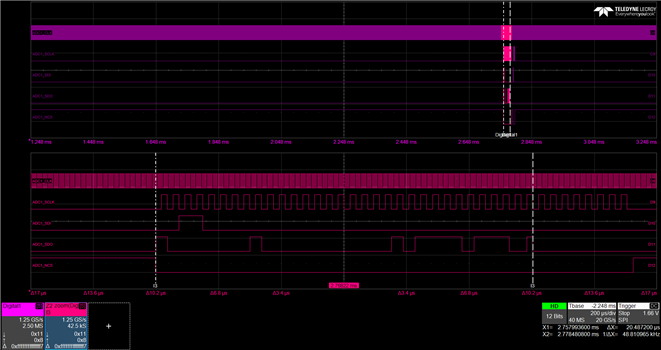

我使用的是 ADS1258。 CLK 频率为12.5MHz、SCLK 频率为1.5625MHz。

ADC 以自动扫描模式运行。 TE 寄存器条件配置 如下:

CONFIG0 0x56

CONFIG1 0x40

MUXSCH 0x00

MUXDIF 0x3F

MUXSG0 0x00

MUXSG1 0xF0

SYSRED 0x00

GPIOC 0x00

GPIOD 0x00

顺序如下:

1.写入 ADC 配置

2.发送脉冲转换命令0x80

3.等待转换

4、读取通道数据0x30

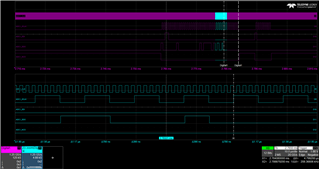

我看到即使 SCLK 处于活动状态、SPI 接口有时也会进入复位状态、缺少通道数据值的最后一个字节。

SPI 在 µs 开始后~20、84 μ s 进入复位状态、即256个 fclk 周期。

从数据表中、我了解到、在 SCLK 处于运行状态时 SPI 接口不应进入复位状态。

您以前是否观察过此行为?