您好!

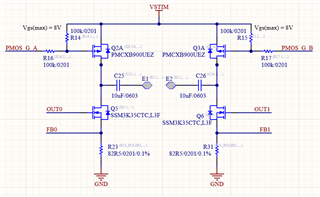

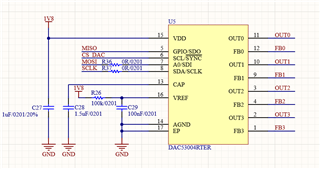

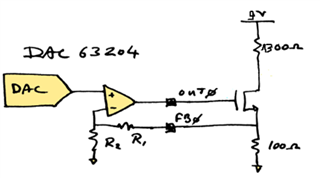

我正在使用 DAC53004通过 MOSFET 的强制检测配置控制负载中的电流:

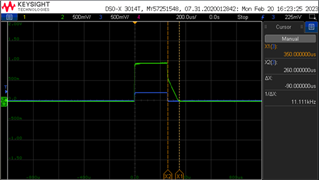

我们正在执行50us/250us 脉冲、中间大约20ms 的休息时间。 一旦脉冲完成、我们将 DAC-X-DATA 寄存器设置为0并降低9V (因此 Vd = 0V)。

这意味着当我们切断9V 时、FB0为0V。 此时、我可以观察到 OUT 信号呈斜坡下降趋势。 我在数据表中找不到有关此行为的任何解释。 我希望它能够更快地降低至0V。 这是我看到的:蓝色表示 FB0、绿色表示 OUT0。

你对此有什么解释吗? 是否可以通过某种方法使 OUT0更快变为0V?

此致、

Aur é lie.