您好、团队成员:

我收到了客户的问题。

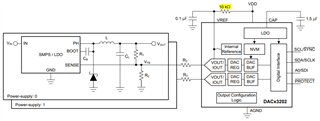

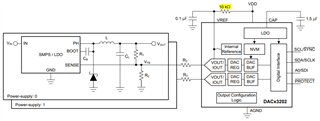

在8.2典型应用中、一个10kΩ Ω 电阻器被插入到 VDD 和 VREF 之间、如果没有这个电阻器有什么问题吗? 客户似乎已经参考典型应用配置了电路、但他说即使向 VDD 施加5V 电压、VREF 处的电压也是4.6V。 这种情况有什么可能的原因吗?

此致、

Masa.

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好、团队成员:

我收到了客户的问题。

在8.2典型应用中、一个10kΩ Ω 电阻器被插入到 VDD 和 VREF 之间、如果没有这个电阻器有什么问题吗? 客户似乎已经参考典型应用配置了电路、但他说即使向 VDD 施加5V 电压、VREF 处的电压也是4.6V。 这种情况有什么可能的原因吗?

此致、

Masa.

您好 Katlynne:

感谢您的支持。

DIS-MODE-IN 位是否设置为1? [/报价]客户设置为0。 使用外部基准时、是否需要将此设置设置设置为1?

基准引脚具有192k 输入阻抗,因此4.6V 可能来自该输入阻抗和10k 电阻器之间的分压器。如果存在192k 阻抗、如果我不在其上放置10k 上拉电阻器是否重要? 请告诉我、我是否有任何理由应该戴上它。

此致、

Masa.

[/quote]

尊敬的 Masa-San:

应将 DIS-MODE-IN 位设置为1以尽可能减少泄漏、但我不认为这是问题的根源。

如果他们使用的是10k 上拉电阻器、那么我认为这可能 是问题所在。 它会导致一个具有引脚输入阻抗的分压器、我想他们从引脚上的4.6V 看到了这个阻抗。

在使用外部基准时、不应使用上拉电阻。 该建议 是在使用内部基准时提出的、因此该引脚不会悬空。

此致!

Katlynne Jones