Other Parts Discussed in Thread: DAC3174, CDCE62005

主题中讨论的其他器件: CDCE62005

大家好、

我的客户遇到了问题:

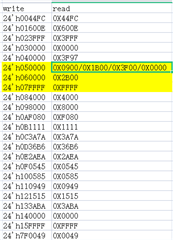

DAC1和 DAC2类似物的输出信号不是同步的(具有同步双通道输出的单芯片)。 目前、FPGA 输入 DA1和 DA2的 DATACLK 和 DATA 信号均处于在 DAC 芯片引脚上测量的同步对齐状态。 同步1和同步2信号对齐(脉冲上升沿)、ALIGN1和 ALIGN2信号也对齐(脉冲上升沿)。 模拟输出中存在相位差。 数据表中关于如何使用对齐信号的说明并不十分清楚。 如果我想实现两个 DAC 的同步输出、我可以进行什么修改吗?

具体来说、DAC 采用默认寄存器状态模式、即正常双同步模式。 上电后、DAC 复位 、然后开始以默认模式工作。

我阅读了文档 https://www.ti.com/lit/an/slaa584/slaa584.pdf、但仍不知道 我是否想确保 DAC 模拟输出没有差异、我应该进行什么配置? 您能为我提供参考文件吗?

您能 提供技术支持吗?

此致、

Katherine