Other Parts Discussed in Thread: ADS8588H

您好!

您能否提供 ADS8588H 的更新数据表? 我们需要官方数据表、指定航空电子项目中用于时序分析的50MHz SCLK 频率。

谢谢。

Matthias

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

尊敬的 Cole:

我们将通过串行接口使用 ADS8588H、OSR=0 @ 500kSPS →2µs 周期时间。 请确认在更新数据表时将考虑以下各项:

此致、

Matthias

尊敬的 Matthias:

我们收到了团队的一些回复。

tCONV 太短,无法仅在繁忙的高电平时间对 SCLK 频率为50MHz 的所有通道执行"转换期间读取"的串行数据。 这就是为什么我们已经实现了在 CONVST 的上升边沿前的数据读取开始、这样就满足了 tDZ_CSBSY 的要求。 因此、CONVST 的上升沿发生在数据读取期间。 根据7.4.1.5章节、"无论 CONVSTA、CONVSTB 引脚的状态如何、都可以从器件读取输出数据、因为器件性能不会下降"。 请确认、这也适用于 CONVST 的上升沿、并且可以忽略 TD_CSCN 并将其从数据表中删除。

[注释] 我无法准确地显示 CONVST 客户何时开始读取数据。 该器件确实支持在相对于 CONVST 的任何点读取数据、而不会影响性能。

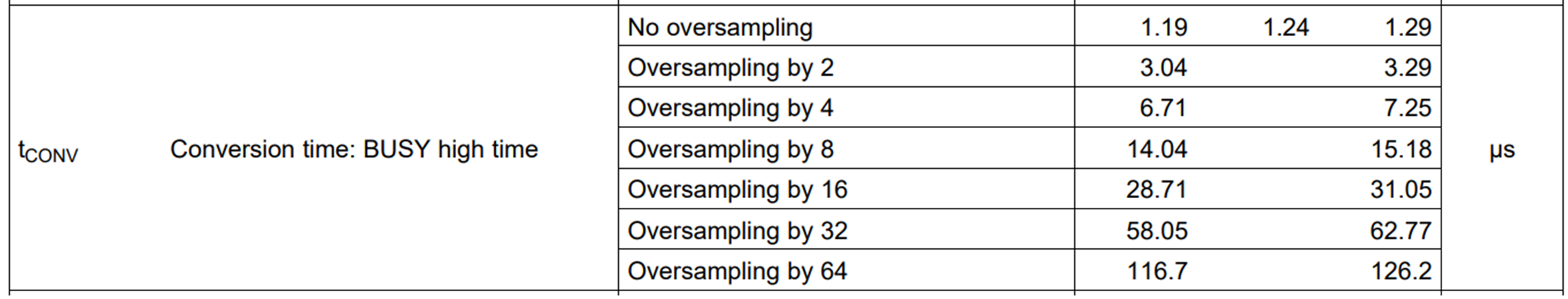

当 CONVSTA 和 CONVSTB 连接在一起且 OSR=0或 OSR=2时,最大值为 td_CNBSY + tCONV + Tacq 的和略高于2µs μ s 周期时间。 请说明 Tacq 在使用通用 CONVST 时是否适用,如果适用,请将请求的 Tacq 值(如0.6µs μ V)减小。

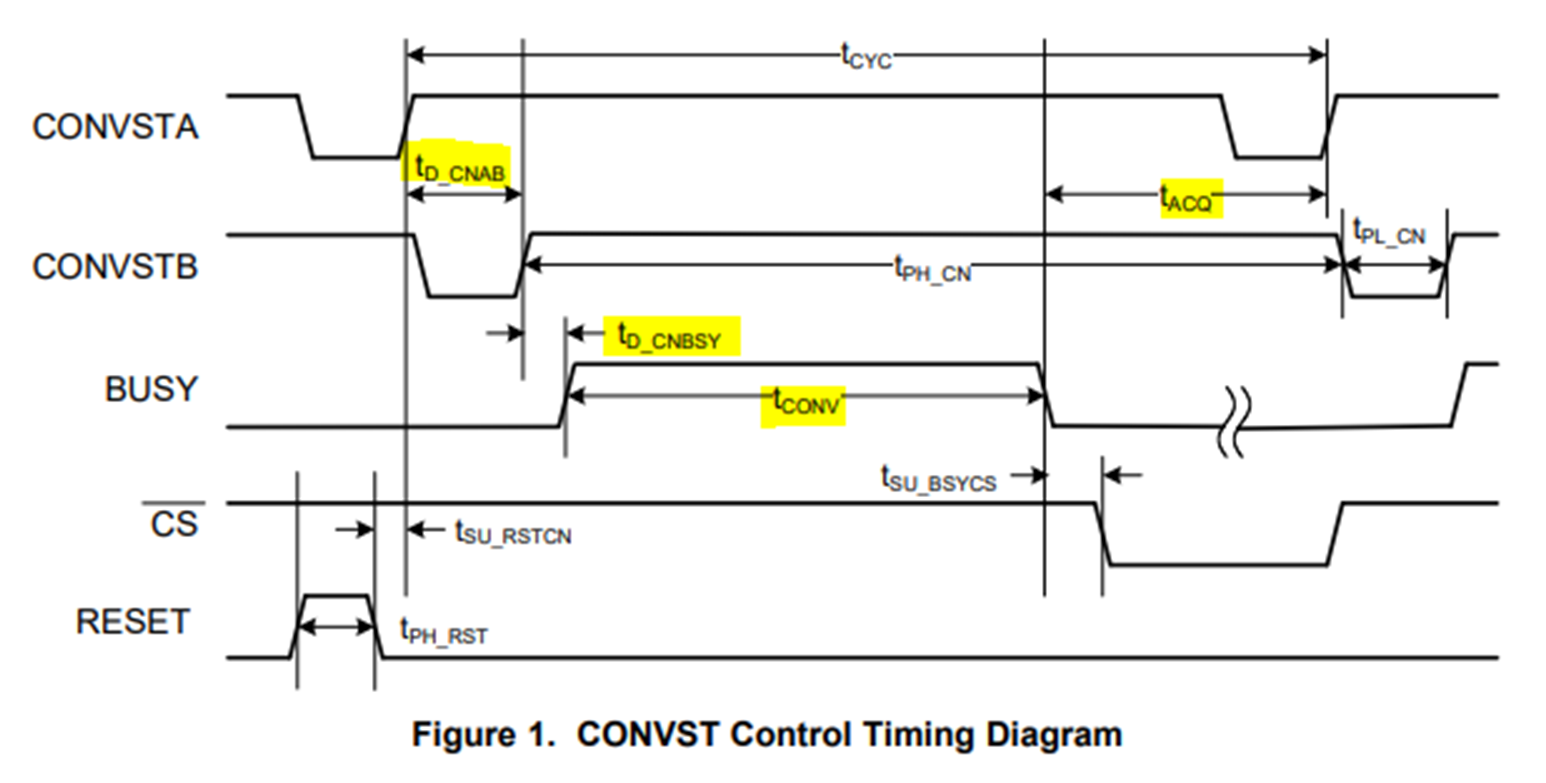

[注释] 如果您参考 CONVST 时序规格图、总周期时间为4个规格的总和。 在下面突出显示的波形中、当 CONVST_A/B 连接在一起时、TD_CNAB = 0。 如果我将所有其他规格的最大值相加、总时间为2.005μs μ s。 我知道这仍然超过了500kHz 采样率所需的周期时间。 但是、必须考虑到 BUSY 信号是 ADC 的输出来响应 CONVST 信号。 因此、ADC 转换在 BUSY 信号变为高电平之前开始(数字输出缓冲器延迟通常为~5ns-10ns)。 因此、在 BUSY 信号变为低电平之前、采集时间实际上开始~5ns-10ns。 数据表中未显示这部分内容;不过、这是它的工作方式。 CS 下降沿仍必须跟随 BUSY 下降沿、不能假设输出缓冲器延迟为5ns-10ns。 简短答案:将 CONVST_A/B 连接在一起、为这个网络计时500kHz。

请删除或更正图71的繁忙时段。

[注释] 我不确定图71中繁忙时段所期望的校正。 它似乎与规格表相同。 请说明。

此致!

-Cole.

尊敬的 Cole:

非常感谢团队的快速响应。

此致、

Matthias

尊敬的 Matthias:

此处是驱动程序中实施的时序的粗略示意图,

现在仍在处理这个。

好了,我们将连接 CONVSTA/B 并将此网络的时钟频率设置为500kHz。 请确认减少采集时间仅影响保持电容的充电(没有几 ns 相关)、而不会影响到在 CONVST 提前发生时任何未就绪的时钟电路。

我已经确认它只影响保持电容器的充电。

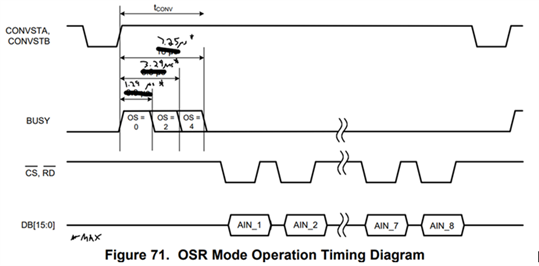

根据我的理解,图71显示 tCONV = 3.8µs @ OSR=0,8.6µs @ OSR=2和18µs @ OSR=4。 这些值超出了第6.15节中的表给出的范围、您在上一个答案中已经显示了该范围。 我错了吗?

我已经确认图71中的数字是错误的、表格是正确的。 在更新后、看上去应与此类似:

此致!

-Cole.

尊敬的 Matthias:

余量足以满足 tDZ_CSBSY 要求。 但未满足 TD_CSCN 要求、则保证金为负。 请从数据表中删除 td_Cscn 要求、因为根据您的解释、没有理由要求" CS 上升沿至 CONVSTA、CONVSTB 上升沿之间的延迟"。

实际上、我对规范的解释与您的解释相同、但是、我没有阅读规范描述以了解其含义。

解释 TD_CSCN 规格的另一种方法是" CONVSTx 上升沿和 CS 上升沿不能彼此相差10ns "。 如果您在下一个 CONVST 之前将 CS 切换为高电平(如图所示)、或者在 CONVST 之后将 CS 切换为高电平(如时序图所示)、这并不重要。 10ns 是最小值、并且上升沿之间的时间几乎为1us、因此满足规范!

希望是有意义的。

应该是一切。 如果您有任何其他问题、请告诉我。

此致!

-Cole.

尊敬的 Cole:

好的。 如果是、请在数据表中添加此澄清说明。 "对我来说,这是一件很奇怪的事。" (可能我有点困惑、因为我在数据表中看不到延迟时间和设置时间的明确区分。 tDZ_CSBSY 被称为延迟时间、而 Tsu_BSYCS 被称为建立时间。 tDZ_CNCS 和 td_Cscn 都被称为延迟时间。)

您的回答让我问您的解释是否也适用于 tDZ_CNCS,因为第6.7段表中的等效措词。 是否应将" CONVSTA、CONVSTB 上升沿至 CS 下降沿之间的延迟"理解为"CS 下降沿和 CONVSTx 上升沿之间不能处于10ns 内"? 如果是这样、tDZ_CNCS 和 TD_CSCN 可以组合到一个时序参数中、提示"CS 边沿(上升或下降)和 CONVSTx 上升沿之间不能在10ns 内"。 因此、CONVSTx 的这个上升沿似乎有一些特殊之处。 允许 SCLK 边沿近距离接触、但 CS 边沿(上升沿和下降沿)不相邻。 为什么? 如果没有说明、这很难理解、因为输出寄存器会在 BUSY 的下降沿附近更新。

我还想提一点。 数据表中显示"CONVSTA、CONVSTB 信号可在内部转换结束时被拉低、由 BUSY 信号指示(请参阅 BUSY (输出)部分)。" 但是、无论是时序要求表还是时序图中、都没有要求 CONVSTx 仅在 BUSY 的下降沿之后变为低电平。 相反、TPH_CN 被指定为最小25ns 因此、数据表中的文本似乎过于限制、应进行调整。

此致、

Matthias