主题中讨论的其他器件: SN74LVC8T245

你(们)好

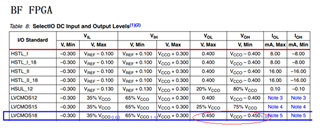

我们正在设计 FPGA 以控制 AFE5828、这是有关 IO 标准电压电平兼容性的问题。 FPGA IO 输出引脚是 LVCMOS1V8 (JESD 8C.01 )标准,可直接连接 AFE 的1.8V 逻辑输入(如 RESET、PDN_GBL、..... 和 SEN、SCLK、SDIN 等)。

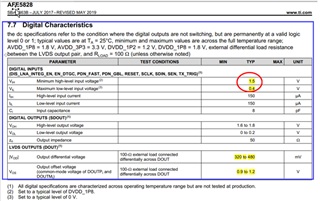

下面是我循环输出时 AFE 和 FPGA 的电压电平、似乎有这种电压电平 风险 FPGA 的 Vol (最大0.45V)> AFE 的 Vil (最大0.4V)、FPGA 的 Voh (最小1.35V)< AFE 的 Vih (最小1.5V)。 这意味着 在某些边界条件下、AFE 可能无法接收正确的逻辑输入。 你怎么看?

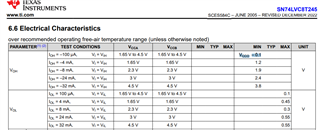

一种 可能的解决方案是插入一个逻辑缓冲器(1.8V 至1.8V),例如 TI SN74LVC8T245。 但是、其 VOL 和 VOH 取决于负载电流(如下图所示)。

那么、我们如何根据 AFE 的1.8V 逻辑输入参数、尤其是 AFE 的 SPI 输入(SPI 在20MHz 频率下工作)来估算负载电流?

顺便说一下、AFE5828的1.8V 逻辑输入/输出是否符合 JESD LVCMOS1V8标准?

非常感谢。