主题中讨论的其他器件:ADC3683、

我们一直将 ADC3683开发板(ADC3683EVM)与 FPGA 搭配使用、我们已设置为通过 LVDS 从 ADC3683接收数据。 通道 B 未端接、当前未被设计使用。 观察到通道 A1在18位恒定图形集之后生成一致但错误的数据。

在调试过程中、LVDS 线路 DA1_P 和 DA1_N 未出现接地或任何其他 LVDS 线路短路。 它们提供与位置 E15和 E16上的连接器的正确连接。 所有导通性测试都是在2个电路板断电并彼此连接的情况下完成的。

该芯片通过板载 FT4232H 板载 SPI 进行配置、寄存器在测试过程中会反映其设定值。 在两次测试之间、使用板载复位开关对芯片进行复位、仅设置3个寄存器作为测试模式寄存器、以帮助简化可能出现在配置其他部分中的问题。

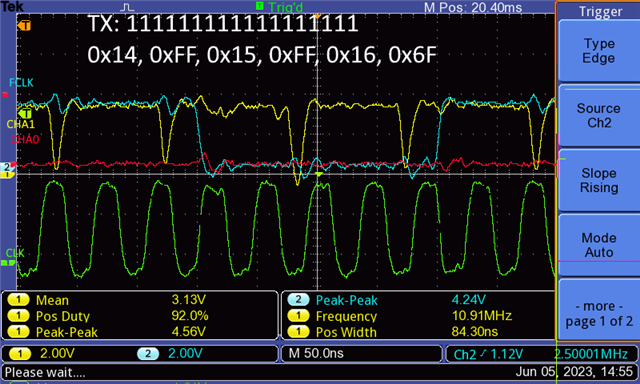

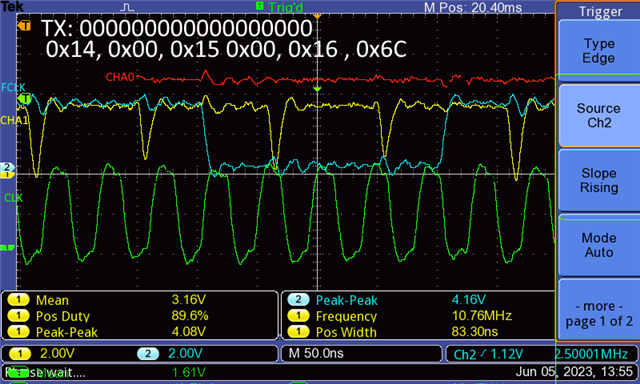

此处记录了两项测试。 第一个是在下一个测试中先发送所有1、然后发送全零。 在此通道期间、A0反映了寄存器中的数据集、而 A1则反映了似乎是4位数据。

所提供的2个图像显示了尝试传输的数据、用于设置数据的 SPI 命令以及每个信号。

这种奇怪的 A1行为看起来与我们所有其他测试都是一致的。 随时欢迎进一步测试或获取有关设置或问题的更多数据、以跟踪问题根源。 感谢您花时间帮助解决这种奇怪的行为。