您好!

我正在创建一个使用 DAC8718的显示驱动程序项目。 我在同步模式(LDAC 触发)下使用单极配置。

此时我遇到2个问题:

1) 1)当输出当前设置为0V 并且我想将其更改为另一个值时、在 LDAC 置位后、输出开始上升之前存在延迟。 仅当前一个输出介于输入代码0x0和0x200 (约)之间时、才会发生延迟。 延迟取决于输出在之前处于低电平的持续时间、介于1至2微秒之间。 延迟太长、我无法达到系统的时序要求。

在数据表中、我发现 DAC 的输出只能保证高于 VSS 0.5V 以上、在本例中为0.5V。 但是、我对设置为0x0时的输出电平很满意、并希望尽可能继续使用该输出电平。 此外、虽然我自己可以避免使用低于0x200的 ADU 值、但我有一个客户、最终能够将其设置为任何值。

因此、我将研究我的其他选择、以避免这种延迟效应并打造稳健的最终产品。 建议的处理方法是什么?

2)当输出比之前更低的值时、DAC 的输出以2个不同的压摆率下降。 首先、输出在大约5V/us 的压摆率下快速下降(足够接近于数据表中6V/us 的值)、但是之后、压摆率会大幅度减慢以达到新的输出值。 它根本不是预期的衰减、看起来与数据表中的图形不同。

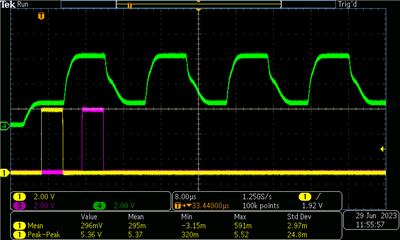

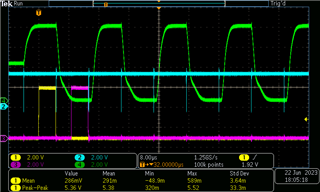

在下图中、我同时显示了这两个问题:

绿色曲线:DAC 输出

蓝色曲线:LDAC 信号

黄色和紫色曲线:显示驱动程序的扫描线0和扫描线1。

您可以看到、当 LDAC 置位时、DAC 的输出立即开始变化、除非之前的输出为0、那么会有1-2us 的延迟。

还显示了压摆率、该问题仅在下降沿发生。

所描述的所有问题都发生在 DAC 的全部8个输出上、并且也会在系统中的其他 DAC 上重复出现(有多个)。