Other Parts Discussed in Thread: LMK04828, ADC32J25, ADC32J24

主题中讨论的其他器件:LMK04828、、 ADC32J24

您好!

现在我们有了电路板、并且已经过验证、包括通过 LMK04828和 FPGA 生成时钟

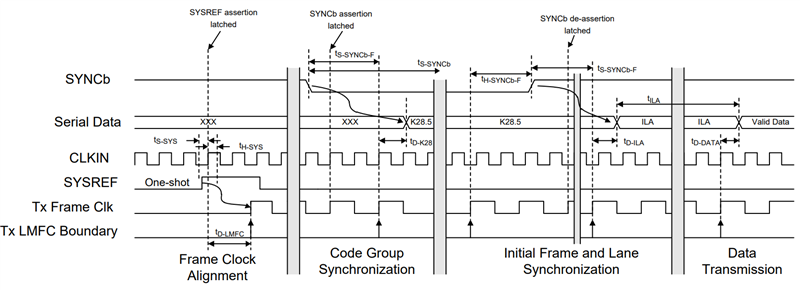

我们现在要尝试使 JESD204B 在 ADC32J25和 FPGA 之间正常工作。

我们将利用以前使用的具有 JESD204B 的 FPGA 设计。

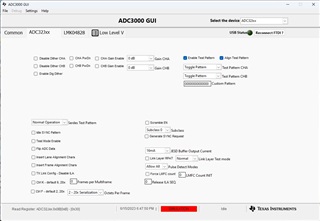

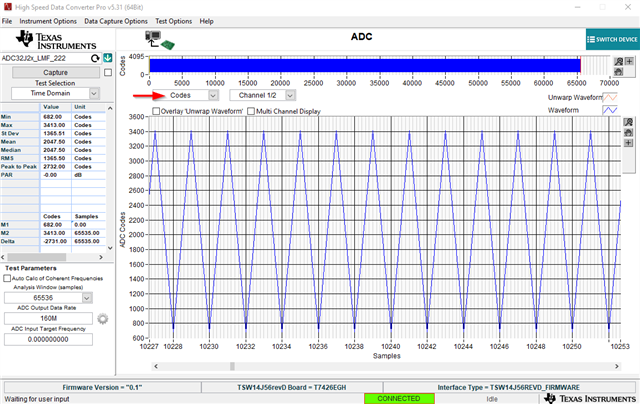

第一步是查看我们是否可以从 ADC32J25接收测试模式。

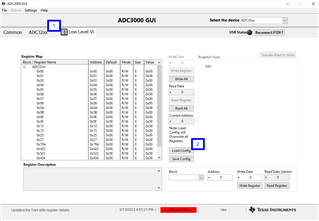

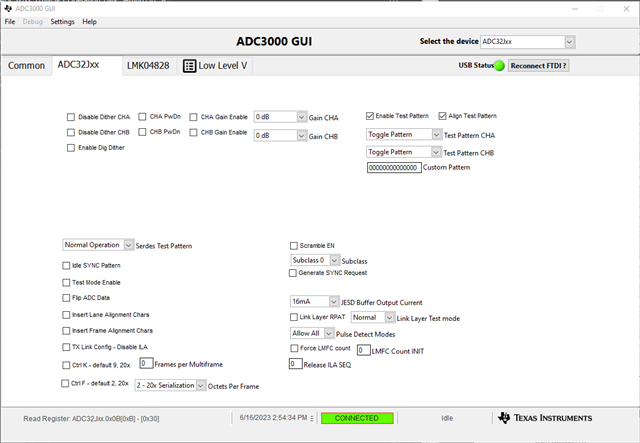

附件是 ADC 寄存器配置。

您能不能看一看配置?

此致、