Other Parts Discussed in Thread: ADC3660

好了、我们来手动操作 ADC3660。

三态缓冲器使能位于 GPIO 引脚上。

我按照数据表中的规定摆动位、而不执行任何操作。

无法判断是否成功写入、并且可以看到读取失败。

那么、打开 ADC3660s SPI 寄存器的最少软件步骤是什么?

P.S.在 ADC3660上使用3线 SPI 有什么优势? 对于器件上的8个无连接引脚、您当然有了空间。 现在零支持你没有任何人做任何好处。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Other Parts Discussed in Thread: ADC3660

好了、我们来手动操作 ADC3660。

三态缓冲器使能位于 GPIO 引脚上。

我按照数据表中的规定摆动位、而不执行任何操作。

无法判断是否成功写入、并且可以看到读取失败。

那么、打开 ADC3660s SPI 寄存器的最少软件步骤是什么?

P.S.在 ADC3660上使用3线 SPI 有什么优势? 对于器件上的8个无连接引脚、您当然有了空间。 现在零支持你没有任何人做任何好处。

Thomas、

默认情况下、串行接口处于活动状态、不执行任何步骤。 您指的是哪种缓冲器? 您是否能够测量电源轨上的功耗? 如果是、我个人在调试初始 SPI 问题时会怎么做、看看写入 POWERDOWN 会降低功耗。 如果您无法获得电源电流、则可以写入 DCLK OB 启用 禁用到 DCLK 输出缓冲器。 您应该能够在示波器上测量此值、并且可以看到如果 SPI 写入成功、DCLK 输出将消失。

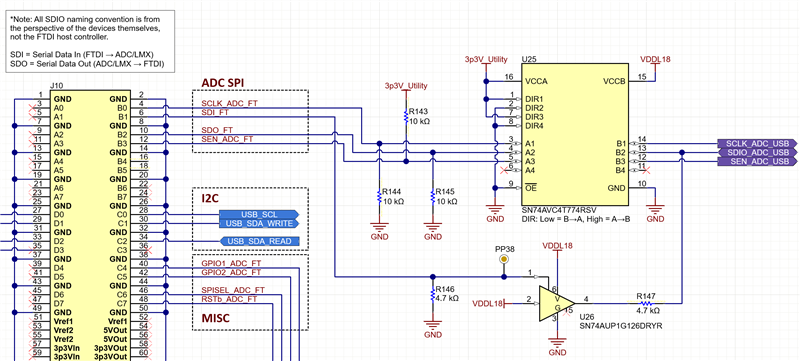

我理解缺少4W SPI 所带来的沮丧。 我自己也喜欢4W SPI。 但该器件是采用相同封装的更大器件系列的一部分、并且该特定器件型号的无连接引脚在其他型号上实现。 大多数客户倾向于3w SPI、这是因为成本高昂的 FPGA 减少了专用于该器件的 I/O 数量、因此设计人员倾向于为所有器件提供3w SPI 接口。 要使用4W SPI 接口、可以在 SDIO 线路上实现三态缓冲、以使用4W SPI 控制器、如以下示例所示。

此致、Chase