您好!

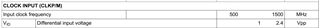

您能解释一下 TI 对 ADC34RF52时钟输入的 VID (差分输入电压)的定义吗? 该规格由制造商的

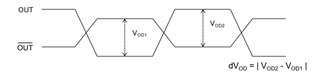

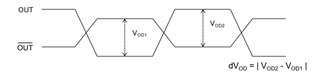

VID 是否从信号本身测量为 VOD、如下所示:

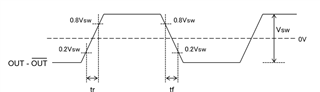

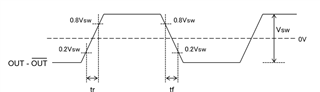

还是通过 ADC 差分放大器的测量结果、差分放大器在将输入信号相加时可以有效地使输出摆幅加倍:

我正在试着确定为了增加 LVDS 而应使用的升压变压器的比率、以便接近2.4 Vpp 的最大规格。

谢谢!

乔

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好!

您能解释一下 TI 对 ADC34RF52时钟输入的 VID (差分输入电压)的定义吗? 该规格由制造商的

VID 是否从信号本身测量为 VOD、如下所示:

还是通过 ADC 差分放大器的测量结果、差分放大器在将输入信号相加时可以有效地使输出摆幅加倍:

我正在试着确定为了增加 LVDS 而应使用的升压变压器的比率、以便接近2.4 Vpp 的最大规格。

谢谢!

乔

您好、Joe!

VID 将作为正负对之间的差值进行测量。 您发布的第一张图片显示了这一点。

对于此器件、时钟应交流耦合并且在 ADC 侧自偏置、 差分时钟输入的每一半应在移位 LVDS 共模周围具有最大1.2V 的摆幅。 例如、如果您在每条差分线路上有一个0.8V 的共模、每条线路的摆幅应为 ±0.6V (0.2V 到1.4V)。 这会在差分信号的一半上产生1.2Vpp 摆幅。 由于差分对的每一半都是180°异相、因此在2.4Vpp 下、总差分电压将是此值的两倍。 这是否有助于消除任何混淆?

此致、Chase