主题中讨论的其他器件: LMK04828

尊敬的 TI 专家:

我的客户之前询问过 ADS54J69、但响应延迟了几天。

您可以查看此问题的状态吗? 时间表非常紧迫。

此外、请检查另一客户与 FPGA 结合的项目。 如果您能给我一些相关的例子、那将会很有帮助。

此致、

蔡斯

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

尊敬的 Amy:

感谢您的支持。

实际上、在我的客户首次开始评估时、我们有2个 cfg 文件。 下面是2个 cfg 文件;

e2e.ti.com/.../2604.ADS54J69_5F00_2x_5F00_dec_5F00_lowpass_5F00_4222.cfg

e2e.ti.com/.../8233.LMK_5F00_Config_5F00_Onboard_5F00_1000_5F00_MSPS_5F00_FPGA_5F00_100M.cfg

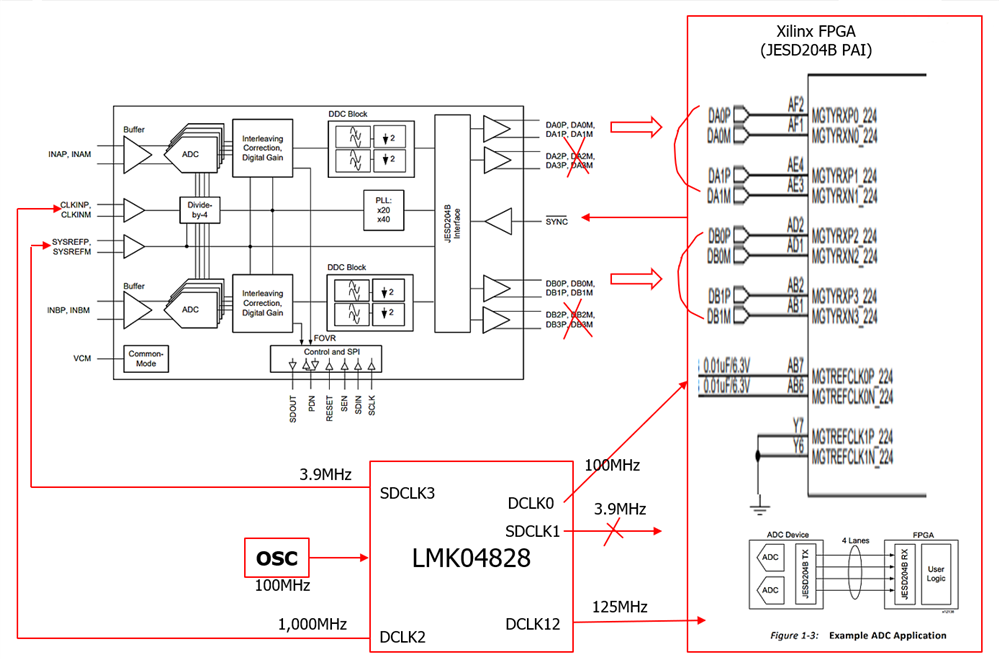

首先、我的客户使用 ADS54J69和 JESD204B 设置、如下所示;

以下是问题;

1.请检查2个 cfg 文件、该文件表示整个设置均为 ADS54J69+LMK04828和 JESD204B (Xilinx FPGA 的 IP) LMFS 4222配置。

(我的客户将外部 OSC 更改为100MHz、请参考其他 TI 工程师的建议。)

2.在上述设置中,连接 ADS54J69和 FMC 连接器的 CLK 和 SYSREF 的预期频率是多少?

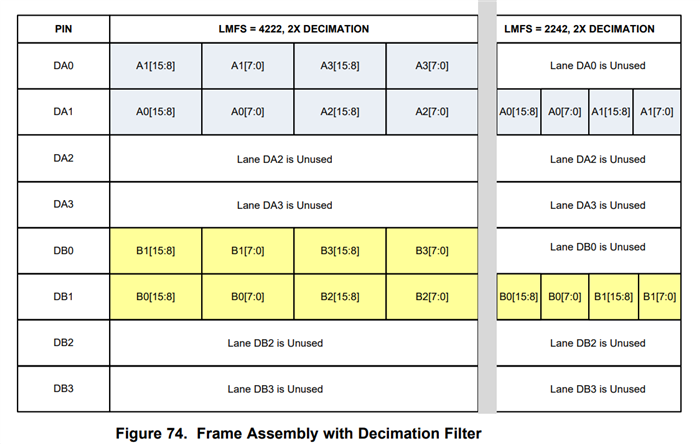

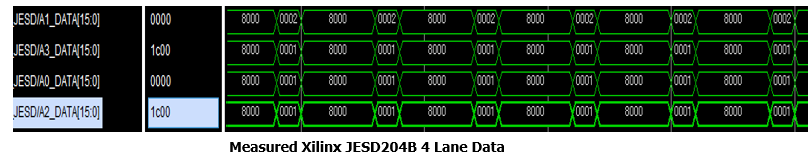

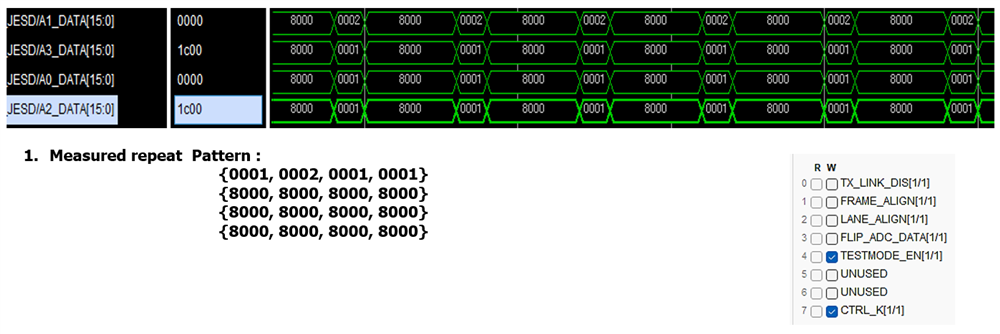

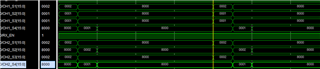

3.使用"ADS54Jxx EVM GUI v1.8"软件设置测试图形模式位(6900位4)。 以下波形测量了 Xilinx JESD204B 4通道数据。 根据 ADS54J69数据表的图74、在模式重复的情况下对其进行了测量、如下所示。

{0,001,000000200000010001}{8,000,80080008000} {8,000,80080008000} {8,000,80080008000}

这个测量数据是否准确? 如果不是、应该测量什么?

请检查此问题。 谢谢

此致、

蔡斯

尊敬的 Chase:

对于问题1、由于 LMK04828中存在分频器、Jim 之前建议根据设计切换到100M 振荡器、以便获得该频率。 此外、我测试了 ADS54J69配置文件并能够获得捕获。 为了便于参考、我在这里附加了两个配置文件、我用于获取基线捕获。

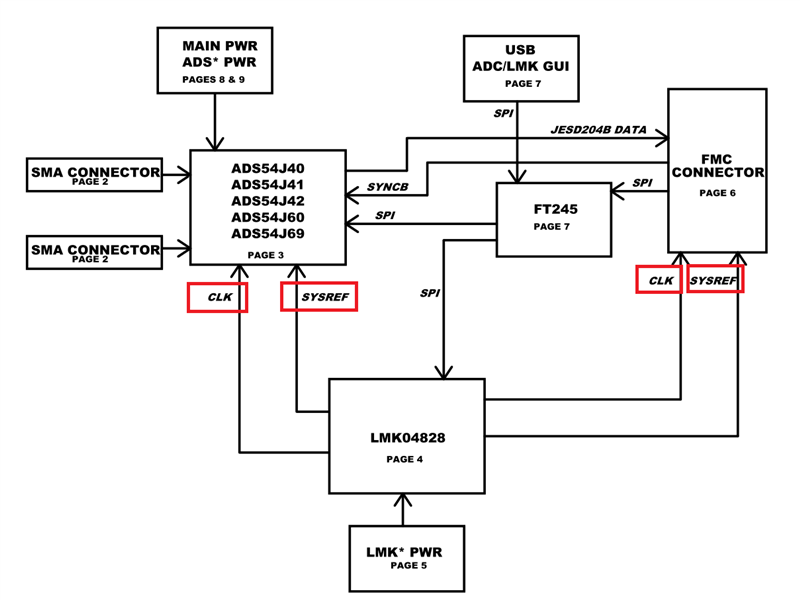

对于问题2、输出频率将基于配置 LMK04828所需的 GUI 设置/寄存器写入(在 GUI 中的 LMK04828 -> PLL2配置下)。 例如、连接 FMC 连接器的 LMK04828_CLK 频率-在我们的 原理图中、振荡器的频率为122.88 MHz。 按照 GUI 结构图、这个频率被乘以12、然后再乘以2、再除以12、得到了246.76 MHz 频率、然后我再次检查示波器。

对于问题3、我看到的测试模式与 Jim Saw 的测试模式不同、因此我将与我们的设计团队就该问题进行核实、然后再与您联系。

此致、Amy

e2e.ti.com/.../7331.LMK_5F00_Config_5F00_Onboard_5F00_983p04_5F00_MSPS.cfge2e.ti.com/.../8688.ADS54J69_5F00_2x_5F00_dec_5F00_lowpass.cfg

尊敬的 Amy:

感谢您的支持。

我的客户又总结了这些问题。 请检查下面的问题。

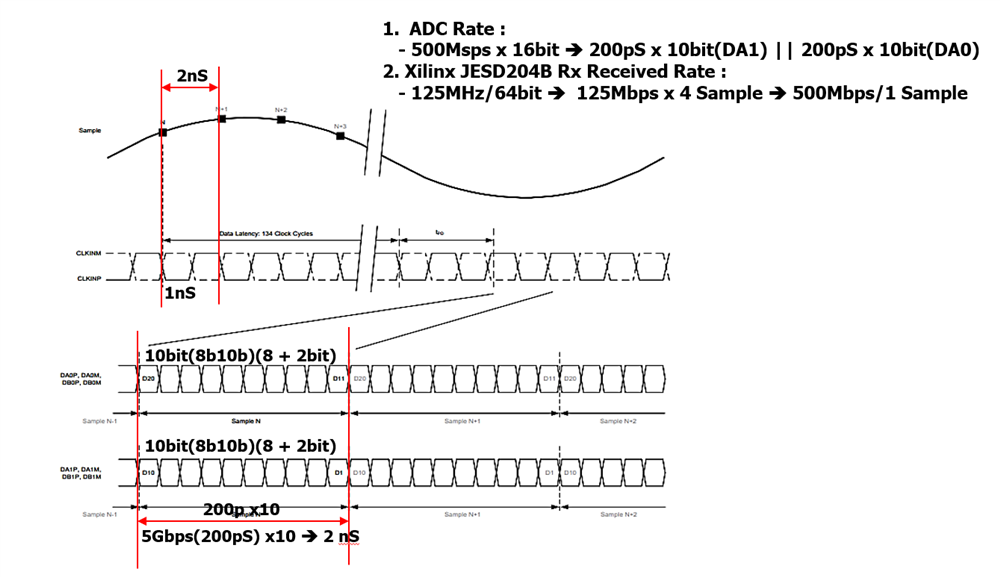

1.关于 ADS54J69 timimg

如果 LMFS4222模式设置为仅使用 DA0/DA1通道、该怎么办。

每个通道都是5Gbps/10位串行输出、这是否正确?

2.关于 I/O 配置

ADS54J69和 LMK04828的 Xilinx FPGA 连接配置如下所示。 是这样吗?

3.关于通过1Gsps 示波器测量时钟

- DCLKOUT0 (FPAG_JESD_CLK):测量的100MHz

- SDCLKOUT1 (FPAG_JESD_SYSREFF):测量的3.9MHz

- DCLKOUT12(CLK_LAO ):测量的100MHz ,但我需要125MHz 用于 Xilinx JESD204B Rx 数据流。 因此、将"CLKout 12和13"更改为32 -> 24

- DCLKOUT2 (CLK ):未测量/可能是1GHz

- SDCLKOUT3 (SYSREF):测量的3.9MHz

-->请确认这些频率是否正确。

4.关于 Xilinx 逻辑示波器测量的测试模式

请确认此测试模式是否正确。

此致、

蔡斯

您好,Chase:

问题1:

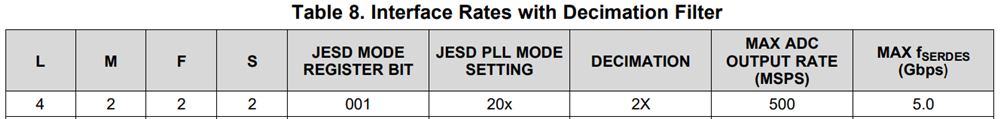

要了解这一点、请参阅数据表第36页的表8。

以最大500MSPS 速率运行、最大 FSERDES 速率将为:

500MSPS -> 2倍抽取率-> 250MSPS * 16位* 1.25 (8b10b)= 5Gbps

(请注意、这适用于通道 A 和通道 B、请参阅数据表中的图74)

问题2:

这些频率看起来没有问题、只需仔细检查它们是否满足 ADC 和 FPGA 的要求即可。

问题3:

我仍在等待设计团队对预期测试图形的回答、但我通过了您的测量图形。

感谢您的发送。

此致、Amy

您好 Amy、

我是 Astel dkkim、他请求技术支持。

您是否确定通道 A (DA0/DA1)和通道 B (DB0/DB1)的四个信号以5Gbps 的速度传输到 FPGA?

FPGA 使用 UltraScale+ Class、而 JESD204B PAI IP 是在5Gbps 4通道模式下设计和运行的。

设置为 ADS54J69测试模式后、已发送的 Xilinx 逻辑探头工具结果以250Mbps 的速度显示。

在 ADS54J69、LMK04828芯片设置脚本文件中是否存在与此现象相关的设置?

希望能快速回复。

此致、

Dkim.

大家好、Dkim、

我向团队确认 SERDES 速率应该为5 Gbps。 您能解释一下您正在测量什么吗?

您正在使用的工具是否可能实际上在测量250Msps 而不是250Mbsps?

如果在1GHz 下输入时钟、然后使用 2倍抽取率 、预计将达到250MSPS。

我已经使用 TI EVM、使用~1GHz 采样时钟在实验室中对此进行了测试、没有问题。

我还在努力从设计团队那里获得有关预期测试模式的答案、我应该在下周早些时候提供一个答案。

此致、Amy

尊敬的 Amy:

我仍在等待预期测试图形数据值。

问题1:为什么检查预期测试图形数据值需要超过一个月的时间、这是 ADS54J69的功能之一?

是否有任何有关 ADS54J69的其他文档?

该项目基于 Xilinx 的典型 JESD204B 应用和 TI ADS54J69 EVM 板开发而成。

同时,发展历史总结如下。

问题2:LMK04828 DCLKOUT12是100MHz。

通常、在5Gbps/4通道方法中、需要125MHz x 4采样才能接收500MSPS 数据。

您为什么在100MHz 中提供脚本?

问题3:请检查您发送的 LMFS222模式脚本文件以重新设置寄存器。

这里总结了到目前为止的发展情况。

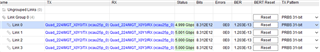

为了检查 Xilinx 串行器/解串器的性能、我通过 Xilinx ibert IP 对其进行了如下验证。

如下面的测试结果所示、Xilinx FPGA 串行器/解串器中4个通道的每一个通道的5Gbps 接收性能都没有问题。

问题4:您能否向我发送与您发送的脚本环境(OSC.= 100MHz、125MHz)相同的 ADS54J69评估环境的经验证结果?

希望您能快速取得成果。

此致、

Dkim.

大家好、Dkim、

我仍在等待我们的设计团队给我提供有关预期测试模式的答案。

我 之前在实验中对此进行了设置、并为您提供了我用于获取基线捕获的配置文件。 不过、我们的 EVM 使用了122.88 MHz 振荡器、因此如果您使用的是100 MHz 振荡器、由于 LMK04828中有分频器、因此您需要考虑这一点。 如果您对 LMK04828的编程感到困惑或需要帮助、请考虑在 时钟论坛中发帖以获得支持。

不过、我可能能够找到解决方案、并会为您进行检查。

此致、Amy

大家好、Dkim、

关于您对测试模式的问题:

请参阅此处的另一个类似帖子以供参考。 Jim 非常擅长解释预期的测试模式: https://e2e.ti.com/support/data-converters-group/data-converters/f/data-converters-forum/679520/ads54j42-ads-54j42

K 参数设置为16、这意味着在 4222模式下、图形将每32个样本重复一次。

我从示例32中的此处开始、图形将在每个多帧中重复一次。

在通道1上、预期的测试图形将显示为:

样本32-33 -> 0x0001 (表示通道 A)

Sample 34 -> 0x0001 (表示来自转换器1的样本1)

样本35 -> 0x0002 (表示来自转换器1的样本2)

采样36-63 -> 0x0000、然后 每32个样本重复一次

在通道2上、预期的测试图形将为:

样本32-33 -> 0x0002 (表示通道 B)

Sample 34 -> 0x0001 (表示来自转换器2的样本1)

样本35 -> 0x0002 (表示来自转换器2的样本2)

采样36-63 -> 0x0000、然后 每32个样本重复一次

此致、Amy

大家好、Dkim、

要回答您的另外两个问题:

问题1:

-> 最大差分输入电压为1.9Vpp (数据表第7页)

->输入信号将围绕共模电压 VCM 摆动。

问题2:ads54J69 16位数字输出格式是有符号输出还是无符号输出?

表39. 寄存器4Bh ->位5 (数据表第53页)表明"默认输出采用二进制补码格式"

如果需要、可以将其更改为偏移二进制输出。

此致、Amy

尊敬的 Amy:

感谢您的快速回复。

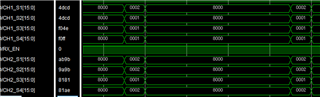

我已针对您发送的预期测试模式分析了测量数据、结果如下所示。

如上图所示、获取数据的概率为10%。

还有一种现象、即每个样本的字节会被交换。

是否有稳定对齐的方法?

D15反转和不稳定对齐现象是否相同?

此致、

Dkim.

尊敬的 Amy:

我会向您发送一个重新测量的绘图文件、

您发送的 CH1预期数据序列为0,001,000 0001000000100000028000… 。

在我发送给你的图表数据,序列是0,002,0001,0001,0001,0001,000,8000,...</s>1000 1000001,000,800

该序列是不同的。

CH2预期数据序列是0,002,0002,0001,0002,8000,8000...</s>2000 100028000800 是的。

您对上述现象有何看法?

此致、

Dkim.

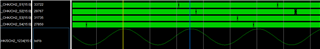

尊敬的 Amy:

我之前发过有关预期模拟信号波的电子邮件、别介意。

如下所示、当输入10MHz 时、1.0Vpp 信号波、

它以如下所示的波的形式进行测量。

SignWave 精确地存储在100ns (10MHz)上、具有2nSx50步长。

如您所知、CH1图案显然存在以下问题:使用 Xilin 204B pai ip 的4个样片订单。

到目前为止,所有问题都已得到解决。

因此、再次感谢您的技术支持。

祝你好运。

此致、

dkkim.