Other Parts Discussed in Thread: DAC38J84, DAC38J84EVM

大家好、

我们客户的一个问题、我将其翻译成了英语、能否提供一些故障排除建议?

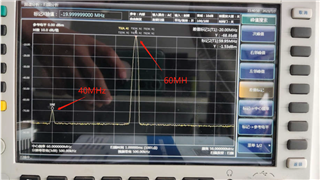

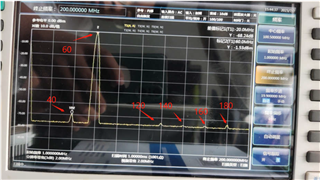

在 DAC38J84测试期间、存在杂散和谐波、杂散的幅度影响了 SFDR。 目前、输出3个70MHz 的 IF 点频信号。 会在这些频率点出现散射点。 通过广泛测试、这些杂散点具有一定的规律性。 下图显示了在频率为40MHz 的60M 下输出时-20MHz 频率偏移的点。 如果 跨度设置为200MHz、则会看到其他谐波和杂散点。 在下图中、在60M 输出时产生影响的点是40M、对 SFDR 有超过10dB 的影响。 其他杂散和谐波信号与信号相差很远、幅值很小且影响很小。 目前、主要需要解决20M 频率偏移处的杂散点。

跨度50MHz

跨度200MHz

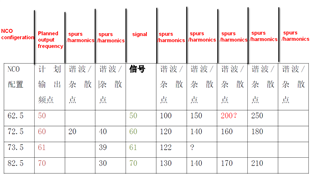

测量多个频率点的结果如下:(__LW_AT__单位:MHz)

DDS 200MHz、信号12.5MHz

表的第一列对应我翻译的红色字体。

表的第一列对应我翻译的红色字体。

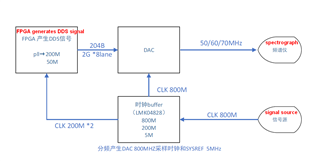

测试环境

FPGA 输出一个 DDS 信号、采样率为200MHz、信号为12.5m。 它通过204B 接口被馈送到 DAC、4次插值后、DAC 与 DAC 的内部 NCO 混合。 混合使用800MHz 采样输出、下图中显示了实际环境:

DDS:采样率200MHz、信号12.5MHz

DAC NCO:请参阅上表

DAC 部件、DAC38J84

目前、使用内插滤波、NCO 和 QMC、同时绕过其他功能

FPGA 使用 IP 内核生成 DDS 信号、采样率为200m、信号为12.5m

分析步骤

1.改变 DAC 的 NCO 后、与 DDS 产生的12.5m 信号混合、杂散点将跟随输出变化、如上表所示

2.更改 FPGA DDS=15.625M、NCO=72.5M、测试结果如下:

3. DDS 输出直流组件,NCO=72.5M

我不熟悉 DAC38J84。 对于此客户解决问题、您能提供一些指导吗?

此致、

罗艾米