Other Parts Discussed in Thread: DAC53204, DAC63204EVM, SN74HCS367

主题中讨论的其他器件: DAC63204EVM、 SN74HCS367

您好!

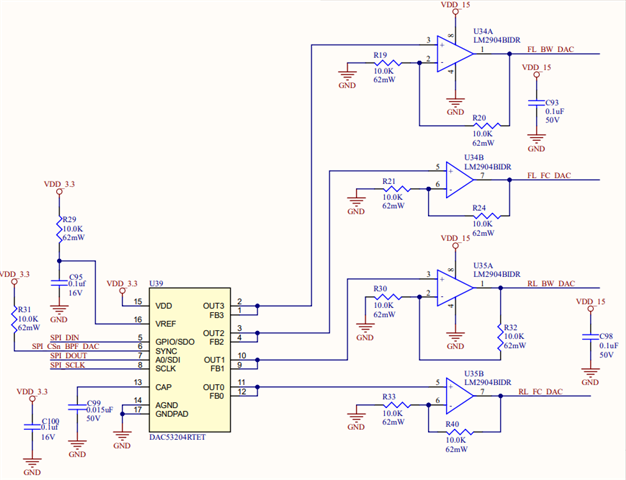

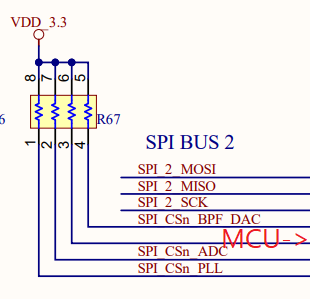

我有一个 DAC53204、我打算在4线制 SPI 模式下使用。 我使用以下编程序列、但看不到预期的结果。

#define DAC53204_REG_COMMON_TRIGGER ((uint8_t) 0x20)

#define DAC53204_REG_GENERAL_STATUS ((uint8_t) 0x22)

#define DAC53204_REG_INTERFACE_CONFIG ((uint8_t) 0x26)

// Unlock device registers

uint16_t reg = 0x5000;

err = write_register(p_handle, chip_select, DAC53204_REG_COMMON_TRIGGER, ®);

// Enable SDO for 4-wire SPI.

reg = 0x1;

err = write_register(p_handle, chip_select, DAC53204_REG_INTERFACE_CONFIG, ®);

// Validate the hardware by checking the ID register (read_register issues a NOP per Figure 7-15. SPI Read Cycle of TRM)

err = read_register(p_handle, chip_select, DAC53204_REG_GENERAL_STATUS, ®);

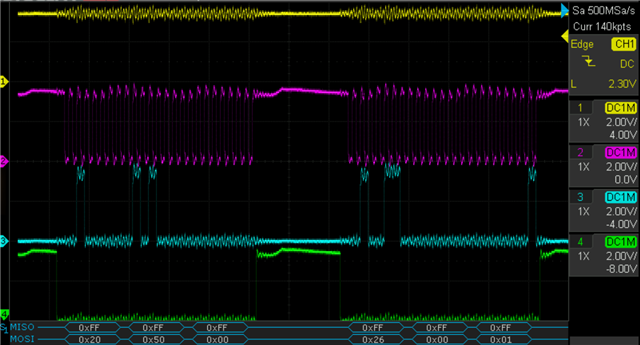

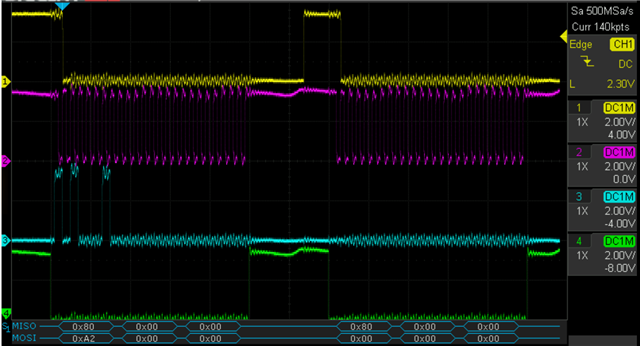

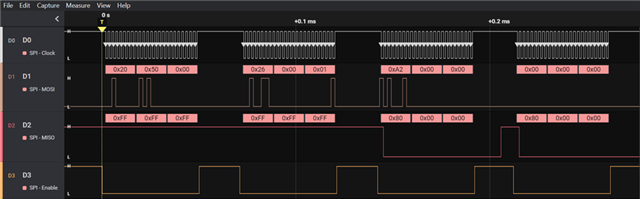

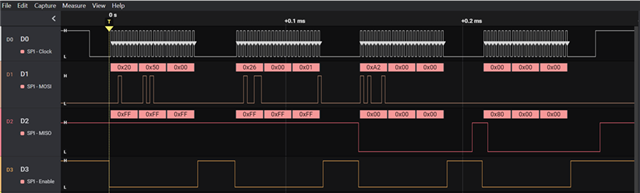

我目前在逻辑分析仪上看到以下内容:

CPOL= 1、CPHA=0

CPOL=0、CPHA=1

在 SDO-EN 位被写入后、我确实看到 MOSI 变为低电平、这根据其他一些 DAC53204文章、似乎是正确的行为。

在任一情况下、我都在最终 NOP 访问中未看到器件 ID (应为 DAC53204:02h)。 我确实看到读取访问的 MSB (位24)和 NOP 在3个不同点设置、但由于这不是读取数据来自何处、因此看起来并不重要。

是否有任何关于我无法读取器件 ID 的见解?

我尝试过0.5MHz 和1.0MHz SCLK 频率。

谢谢。

标记