尊敬的专家:

我最近使用 ADS1274进行4通道采集。 但遇到关于/sync 的一个奇怪现象。

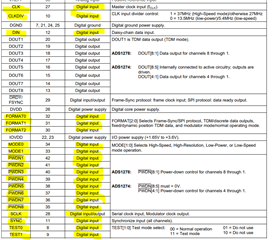

ADS1274处于 SPI/TDM/固定、高分辨率模式。 使用 CLK 频率27M 时、数据速率和/DRDY 频率约为52.7K、如图所示、这很好。 (黄色为 DRDY、蓝色为 SCLK)

此时、/SYNC 引脚悬空。 其电压为~3.3V。

如果我向/SYNC 施加低电压(例如 GND)、/DRDY 将变为高电平、SCLK 消失。 也可以、因为根据数据表、/DRDY 将在/SYNC 下降沿变为高电平、并且我的 MCU 在没有 DRDY 下降沿的情况下不会产生 SCLK。 如果我让/SYNC 引脚再次悬空、/DRDY 和 SCLK 信号恢复正常。

奇怪的 现象 是、如果我对/SYNC 施加高电压(例如 VCC 3.3V)、/DRDY 频率会降低约420Hz、远低于预期的52.7K。 当然、SCLK 在正常/DRDY 下运行良好。

进一步测试后、我发现有些/DRDY 丢失、就像这张图片一样、只捕获了两个/DRDY 信号。

那么、我的问题是如何控制/SYNC 引脚。 如果直接将引脚连接到 MCU 的通用 IO 引脚、看起来好像失败了。

谢谢。