主题中讨论的其他器件:、 ADS1291

您好!

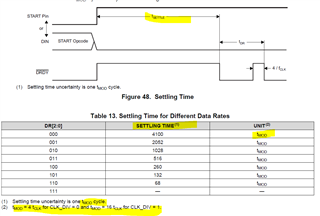

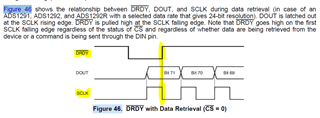

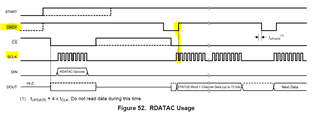

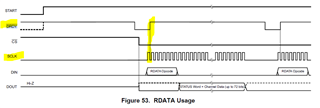

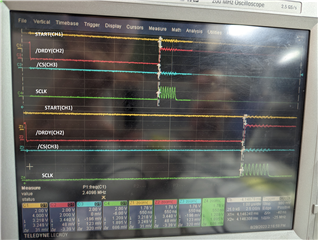

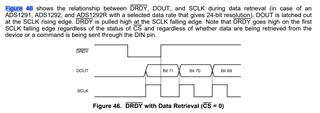

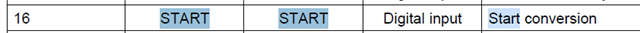

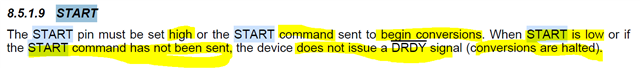

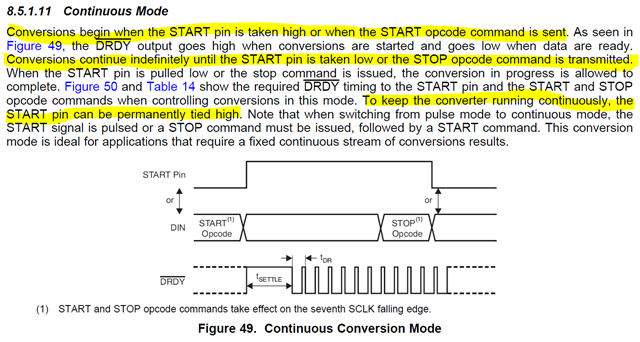

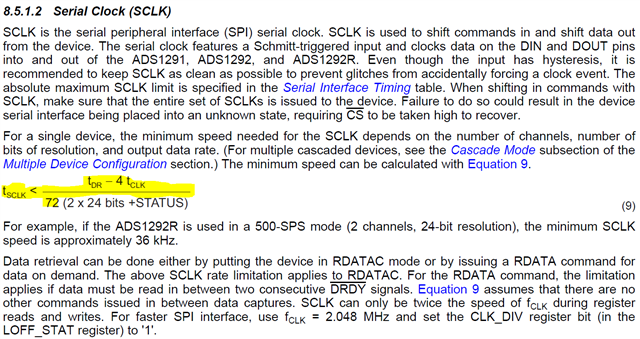

我的客户 遇到了使用上拉电阻器 START=Hi 的 RDATA 命令从 ADS1292采集数据时的问题。 请参阅"AFE Circuit.pdf"如何连接 ADS1292器件(使用2个器件)和"ADS1292 AFE 数据采集问题.xlsx" 、详细说明问题您能否详细说明其系统无法正常运行的原因以及解决问题的方法? 数据表在多个地方显示了/DRDY 和 RDATA、这使我以及我的客户混淆了/DRDY 和 RDATA 的含义。

e2e.ti.com/.../AFE-Circuit.pdfe2e.ti.com/.../ADS1292-AFE-data-acquisition-timing-issue.xlsx

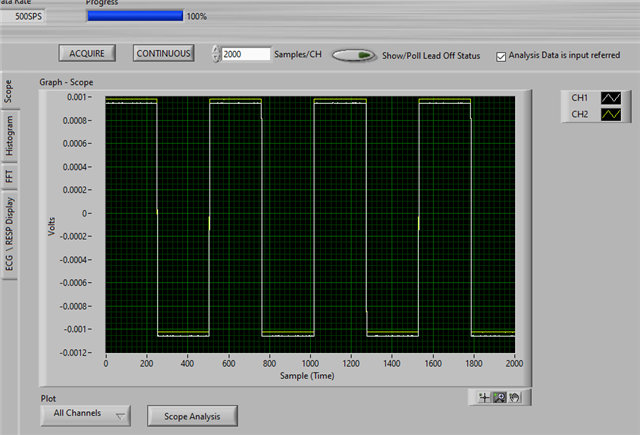

他们似乎有时会读出如下内容。 他们确认了不正确的数据不是噪声。

1 2 3 4 5 6 <-预期

1 2 2 4 5 6

1 2 3 4 4 6

1 2 4 4 5 6

有时他们甚至会读出这样的数据。

1 2 3 9 5 6

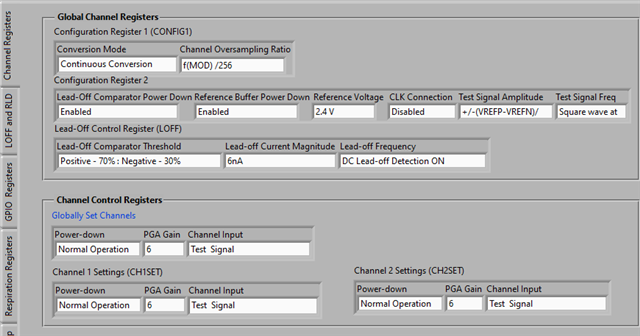

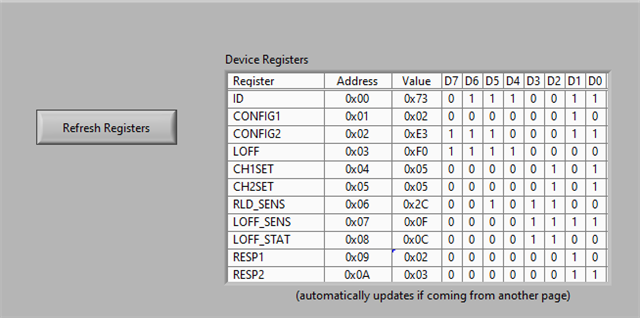

请注意、他们确认了 SPI 的时序没有问题。 另请注意、其系统配置如下所示。

AFE#1

0x02、 // CONFIG1

0xE0、 // CONFIG2

0x90、 // LOFF

0x00、 // CH1SET

0x80、 // CH2SET

0x00、 // RLD_SENS

0x03、 // LOFF_SENS

0x00、 // LOFF_STAT

0x02、 // RESP

0x03、 // RESP2

0x0C // GPIO

AFE#2

0x06、 // CONFIG1

0xA0、 // CONFIG2

0x90、 // LOFF

0x10、 // CH1SET

0x90、 // CH2SET

0x00、 // RLD_SENS

0x00、 // LOFF_SENS

0x00、 // LOFF_STAT

0x02、 // RESP1

0x03、 // RESP2

0x0C // GPIO

此致、

川崎义和