Other Parts Discussed in Thread: DAC3484

您好!

我的客户在满足以下条件的情况下使用 DAC3484。

- DACCLK = 1228.8MHz、插值= 4x

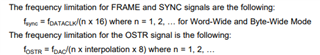

在这种情况下、使用 OSTR = 38.4MHz 和 DATACLK = 614.4MHz 是否正确?

谢谢你。

JH

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好、JH:

对于 Fdac = 1228.8MSPS、4倍内插值、接口速率为368.64MSPS。

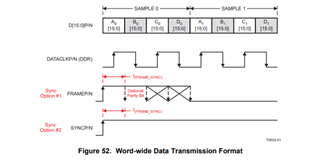

在字宽格式中、总数据吞吐量将为4通道 X 368.64MSPS = 1228.8MSPS、每个通道为16位。 由于是 DDR、因此 DATACLK 的时钟速率在614.4MHz 处是正确的。

FOST = Fdac/(n*4*8)= 38.4/N,其中 N 为整数

是的,您对614.4MHz 的数据记录和38.4MHz 的 Fostr 的计算是可以的。

您好、JH:

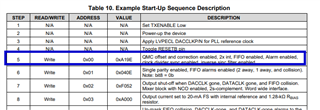

可能存在配置问题。 示例配置适用于2倍内插。 您可以调整 INT 寄存器以适应4倍内插。

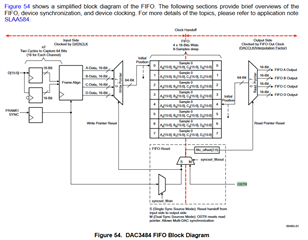

另请参阅以下应用手册第2.3节、以了解有关 FIFO 优化的详细信息: