主题中讨论的其他器件:ADC12QJ800

我们目前正在为其中一款使用 ADC12QJ800的产品开发一种新的数据采集系统

连接到从 zcu102参考设计修改的 TI-JESD204 IP、以适应我们项目中使用的 Kria K26 SOM。

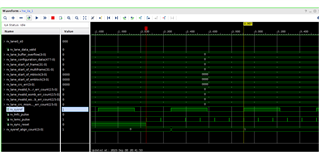

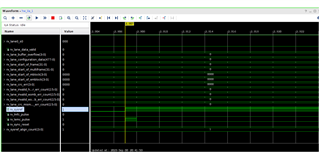

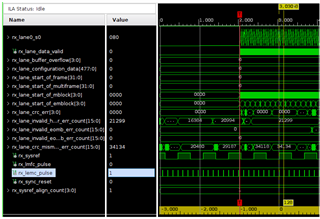

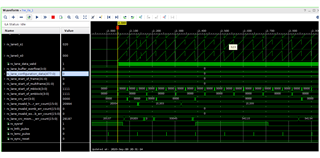

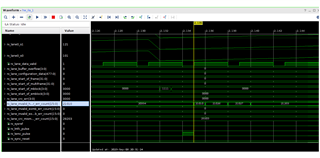

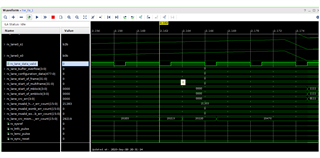

我已成功配置 ADC 和 JESD IP、以12位 ADC 分辨率在800msps 的速率下运行4个通道。 来自 ADC SPI 命令的 JESD_Status 显示链路已接通、但当我释放 JESD 复位时、它并不总是为缓冲器释放值提供引脚。 我已经设置了适当的缓冲区释放延迟。 一些连续复位后、我使 lemc 释放缓冲器、并在停止之前获得一些具有 x 数量数据的有效时钟。 这一切都是在 ILA 能够捕获另一个有效信号之前发生的、因此不长。 我偶尔会遇到一些 CRC 错误、并且我已经运行斜坡测试模式、似乎有时数据中只出现几次毛刺脉冲。 我想知道如何调试和解决此问题、以便获得能够全天候传输数据的可靠链接。 我不确定这是否只是同步问题、而且由于电路板布局布线、我缺少了一些东西或数据完整性问题。 lemc 脉冲与 sysref 对齐、并且似乎继续、而不管有效数据如何、并且似乎从我的所有计算中产生了准确的周期。

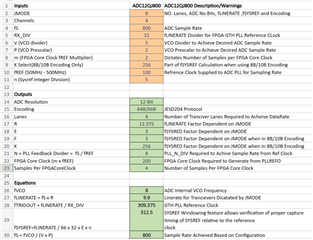

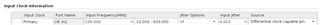

已将 ADC 配置为将差分时钟引脚与板上在 ADC 本地生成的100MHz 参考时钟配合使用。 PLLREFO 随后将该时钟传递给 FPGA、为200MHz 处的 JESDIP/收发器和 FPGA 器件时钟生成 DRP 频率线速率/66= 150MHz 时钟、对其进行采样以生成312.5KHz 参考频率。 Trigout 被编程为309.375MHz 进入 GTH 参考时钟。

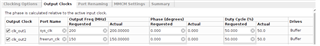

ADC 计算

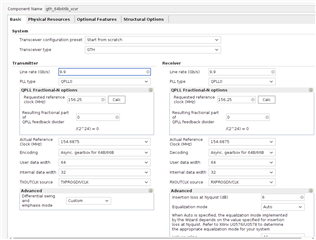

GTH 收发器设置

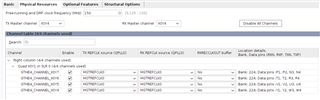

MMCM 时钟配置

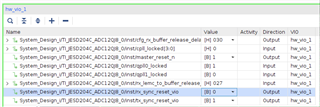

VIO

ILA 复位触发器

ILA 触发数据有效

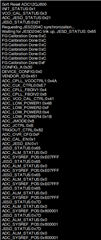

ADC 的 SPI 代码

//软复位

SPI_DATA = ADC_WriteRegister (ADC_CONFIG_A、0xB0、1);

xil_printf ("软复位 ADC12QJ800\r\n");

//等待 INIT_DONE

SPI_DATA = 0;

while (SPI_DATA =0){

usleep(100000 );

SPI_DATA = ADC_ReadRegister (ADC_INIT_STATUS、1);

xil_printf ("init_status:0x%x\r\n "、SPI_DATA);

}

// CPLL 配置

ADC_WriteRegister (ADC_CPLL_RESET 、0x01、1);//复位 CPLL

ADC_WriteRegister (ADC_CPLL_VCOCTRL1、0x4A、1);//VA11Q 和 VCLK11噪声抑制

ADC_WriteRegister (ADC_CLK_CTRL0 、0xE7、1);//SYSREF_PROC&RECV_EN SYSREF_SEL=7

ADC_WriteRegister (ADC_CLK_CTRL2 、0x05、1);//CPLL VCO_BIAS

ADC_WriteRegister (ADC_CPLL_FBIV1 、0x04、1);//VCO/(PxV)= 800MHz (P=2 V=5)

ADC_WriteRegister (ADC_CPLL_FBIV2 、0x08、1);//Fs/Ref=800MHz / 100MHz (N=8)

ADC_WriteRegister (ADC_VCO_CAL_CTRL、0x41、1);//VCO_CAL_EN

ADC_WriteRegister (ADC_CPLL_RESET 、0x00、1);

//停止 JESDC

ADC_WriteRegister (ADC_JESD_EN 、0x00、1);

ADC_WriteRegister (ADC_CAL_EN 、0x00、1);

ADC_WriteRegister (ADC_JMODE 、0x08、1);//JMODE8

ADC_WriteRegister (ADC_JTEST 、0x04、1);//斜坡测试数据

ADC_WriteRegister (ADC_JCTRL 、0x0B、1);//JSYNC_N 有符号2的 扰码

ADC_WriteRegister (ADC_TRIGOUT_CTRL、0x82、1);//TRIGOUT 9.9Gbps/32= 309.375MHz

ADC_WriteRegister (ADC_OVR_CFG 、0x0F、1);//OVR_EN 512Samples

//等待 VCO_CAL_DONE

SPI_DATA = 0;

while (SPI_DATA =0){

usleep(100000 );

SPI_DATA = ADC_ReadRegister (ADC_VCO_CAL_STATUS、1);

xil_printf ("VCO_CAL_STATUS:0x%x\r\n "、SPI_DATA);

}

//等待 CPLL_LOCKED

SPI_DATA = 0;

while (SPI_DATA =0){

usleep(100000 );

SPI_DATA = ADC_ReadRegister (ADC_JESD_STATUS、1);

xil_printf ("ADC_JESD_STATUS:0x%x\r\n"、SPI_DATA);

SPI_DATA = SPI_DATA & 0x01;

}

//启用 JESD204C

ADC_WriteRegister (ADC_CAL_EN 、0x01、1);

ADC_WriteRegister (ADC_JESD_EN 、0x01、1);

ADC_WriteRegister (ADC_ALM_STATUS 、0x3F、1);//清除警报

ADC_WriteRegister (ADC_CAL_PIN_CFG 、0x00、1);//FG_DONE、CAL_PIN_CFG

ADC_WriteRegister (ADC_CAL_SOFT_TRIG、0x00、1);

ADC_WriteRegister (ADC_CAL_SOFT_TRIG、0x01、1);//启动校准

//等待 FG_DONE

SPI_DATA = 0;

while (SPI_DATA =0){

usleep(100000 );

SPI_DATA = ADC_ReadRegister (ADC_CAL_STATUS、1);

xil_printf ("FG 校准完成:0x%x\r\n"、SPI_DATA);

SPI_DATA = SPI_DATA & 0x01;

}

ADC 调试 SPI 状态

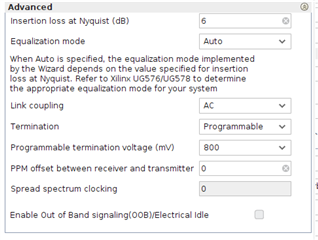

我尝试过配置不同的测试模式、一些测试模式的工作效率比其他测试模式更可靠一些、我还尝试配置500MSps 的测试结果类似、但无论错误看起来如何、我似乎从未得到超过第一组数据、然后就会停止。 当使用 SerDes 预加重的东西似乎变得最糟糕时、我也尝试了 GTH 插入损耗、但它似乎没有太大的区别、因为使它变得更好。 我还尝试了100,200和300 ppm 的偏移、但我认为这些也使情况变得更糟、因此我将其保留为0。

您可以建议哪些内容来帮助了解我遇到的错误、以及如何解析链接以获得连续流?

提前感谢。