Other Parts Discussed in Thread: AFE5828

你(们)好!

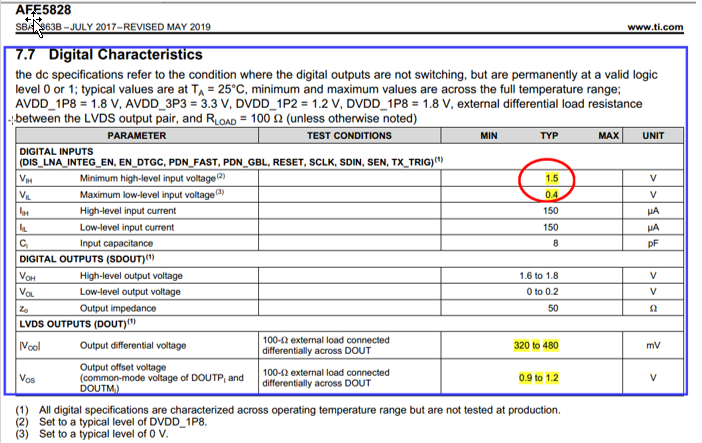

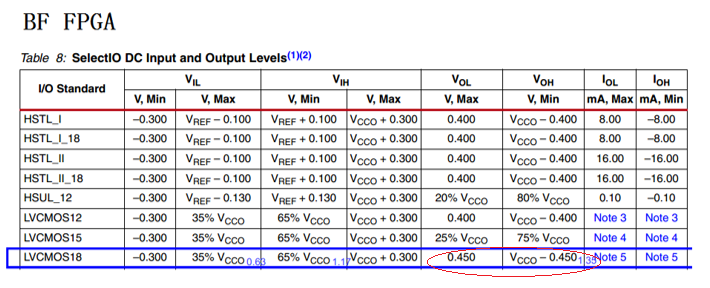

如 pic 所示、FPGA 的 Vol (最大0.45V)> AFE 的 Vil (最大0.4V)、FPGA 的 Voh (最小1.35V)< AFE 的 Vih (最小1.5V)。 这意味着 在某些边界条件下、AFE 可能无法接收正确的逻辑输入。

1.虽然我们可以插入电压电平转换器,以确保它们兼容(我们不想这样做,因为我们认为风险很 低),但我们仍然感到困惑: 由于 FPGA 和 AFE5828都声称它们是 LVCMOS1.8V 标准、因此它们应该能够直接相互连接、而没有任何风险。

2. 请问 AFE5828第7.7节注释(2)/(3)是什么意思?" SET TO xxx"的典型等级? 表中的典型电平为1.5V 和0.4V。

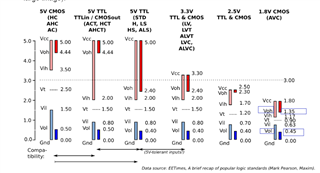

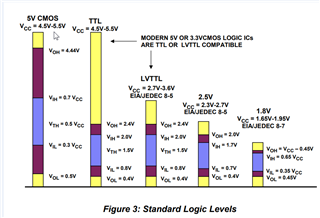

3.顺便说一下,我在网上搜索的 LVCMOS1.8V、VOH = 1.35V、VOL = 0.45V。 但是、 AFE5828是不同的( 更严格?、 1.5V 和0.4V。 )。 您能解释一下吗?

https://www.jsykora.info/2014/05/logic-voltage-levels/

谢谢!