您好、TI!

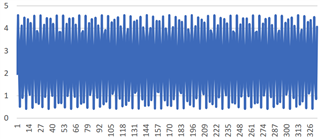

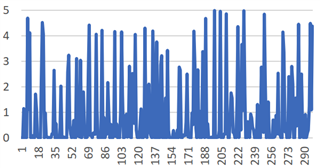

目前、我们正在努力解决其中一种组件在其中一个电子板上产生意外数据的问题。

一些时序问题可能在处理中、但我们希望获得数据表中没有的确切性或确认性。

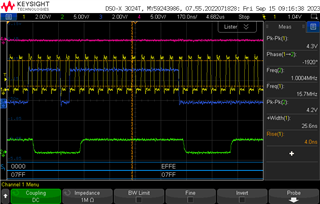

下图以红色显示了我们驱动 DIN ADC 输入的方式:

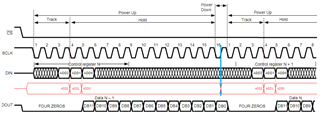

我们对数据表的理解是、DIN 引脚保持和设置时序仅在每个16- SCLK 周期的前8个上升沿受到限制。

"在转换过程中、下一个转换输入的地址被计时到控制寄存器中

在 CS 下降后 SCLK 的前8个上升沿通过 DIN 引脚。 请参阅表1、表2和表3。"

如您在上方所见、DIN 引脚(红色)在这8个 SCLK 上升沿中是稳定的、因此应该不会出现时序问题。

不过、我们当前使用第16个 SCLK 上升沿(以蓝色突出显示)来更新下一个周期的 DIN 值。

由于此更新发生在 SCLK 上升沿的同时、因此我们想知道是否存在设置/保持计时没有遵循控制寄存器计时的风险、即使这发生在前8个上升沿的窗口之外。

这是否会以某种方式导致意外的数据输出?

我们对数据表的第一种解释是、在每个16-SCLK 访问的前8个 SCLK 上升沿之外没有控制寄存器时钟。

你能确认这一点吗?

此致、