请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:ADS1256 主题中讨论的其他器件: REF6025、REF5025

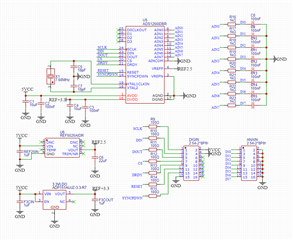

这是我设计的原理图。 是否有任何似乎不合理或需要更正的地方?

我的信号范围为0至20Hz、采样率为200Hz。

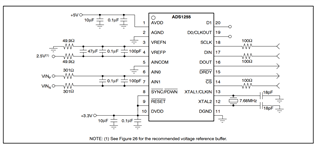

下面是 ADS1256数据表中提供的电路图。 我想知道为什么有这么多去耦电容器连接到 VREF 引脚及其用途。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好、LEO_0916

对原理图的一些想法:

-Bryan