团队成员很好!

我的客户对该 IC 很感兴趣、并且对噪声规格还有进一步的问题。

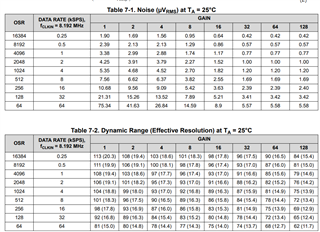

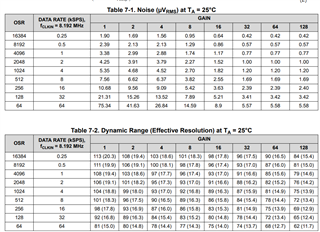

下表摘自第15页。 此时主时钟设置为8.192 MHz。

我知道 调制时钟和滤波器时钟(调制时钟/OSR)对于上述噪声值至关重要。

问题1: 我的客户在2MHz、1MHz、300kHz 时需要噪声值和 DR 值。 这里有一些值吗? 如何计算这些值?

问题2. 您能告诉我们噪声和动态范围与高分辨率模式/低功耗模式/VLP 之间的关系是什么机制吗?

谢谢。

卢克

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

团队成员很好!

我的客户对该 IC 很感兴趣、并且对噪声规格还有进一步的问题。

下表摘自第15页。 此时主时钟设置为8.192 MHz。

我知道 调制时钟和滤波器时钟(调制时钟/OSR)对于上述噪声值至关重要。

问题1: 我的客户在2MHz、1MHz、300kHz 时需要噪声值和 DR 值。 这里有一些值吗? 如何计算这些值?

问题2. 您能告诉我们噪声和动态范围与高分辨率模式/低功耗模式/VLP 之间的关系是什么机制吗?

谢谢。

卢克

Luke、您好!

我看到您对同一 ADC 提出了类似的问题、您可以在以下内容中找到答案:

您能否将客户的姓名输入到上面的"备注"字段中? 谢谢。

此致、

戴尔