似乎数据表仅列出了使用 LVDS 作为 CLK+/-参考时钟输入时的特定规格、而不是特定于 LVPECL 的规格。 它指出、每当 DEVCLK_LVPECL_EN 设置为(1)时、内部终端都变为50 Ω 的接地电阻。 通常、LVPECL 驱动器端接至地、接收器设置为某种共模电压。 或者、接收器使用与 RTT 串联的50欧姆端接网络接地。 您对使用 LVPECL 且具有50欧姆端接(最好是交流耦合)接收器的此器件的端接技术有什么建议吗?

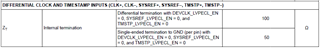

此外、数据表还显示、 当 DEVCLK_LVPECL_EN = 0时、内部终端 ZT 设置为100欧姆、但当 DEVCLK_LVPECL_EN = 1时、ZT 也设置为50欧姆。

但是、进一步到表8-60中、当 DEVCLK_LVPECL_EN = 1时、ZT 变为50欧姆接地端。 我假设表8-60中的文档是正确的、并且建议运行条件中的 ZT 值 是一个拼写错误、除非我缺少什么。