Other Parts Discussed in Thread: ADC12QJ1600, ADC12QJ1600EVM, LMK04828, TSW14J57EVM

主题中讨论的其他器件:、 LMK04828、 TSW14J57EVM

尊敬的 TI 支持团队:

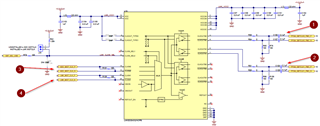

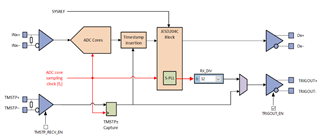

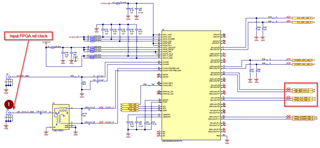

我目前正在从事一个项目、其中涉及将 ADC12QJ1600EVM 开发板与 Xilinx Zynq UltraScale 板(EK-U1-ZCU102-ES2-G)相连接。 我为 ADC12QJ1600设计了 SPI 驱动器、我将在 MicroBlaze 软内核中使用。

我已成功成功通过 SPI 访问 ADC 寄存器。 作为测试、我读取 VENTER_ID 寄存器、它会返回预期值0x0451。

然而、我将面临一个与 C-PLL 初始化相关的问题。 我使用板载50 MHz VCXO 振荡器(Y2)对 SE_CLK 引脚进行计时、并使用以下设置:

JMODE:8

采样率:1GSPS

反馈分压器:V = 4、P = 2、N = 20

我已经验证了50 MHz 时钟是否显示、并且通过使用示波器观察电阻器 R231上的信号来验证时钟是否清晰。 开发上的所有跳线。 正确设置电路板 ADC12QJ1600EVM (包括 OSC 开启、PLL_EN_ADC、PLLREF_SE_ADC)。

我还尝试过通过 CPLL_OVR 寄存器配置基准时钟源选择和启用 C-PLL、但没有效果。

故障排除步骤

*已检查数据表中的 SE_CLK 频率范围(50 MHz 至500 MHz)、因此 SE_CLK 处于该范围内。

*重复所有可能的选项配置 C-PLL 反馈(FS 范围内的500 MHz - 1300 MHz 与参考时钟: 50MHz )

在等待 C-PLL 锁定标志时总是遇到一个超时。

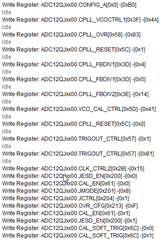

我已经遵循数据表中"9.3初始化设置"段落中建议的寄存器编程顺序、但问题仍然存在。

为了提供更详细的环境信息、我列出了在 ADC 初始化过程中发生的 SPI 事务。 这将提供我已采取的步骤的全面视图、并可能有助于确定任何差异或问题。

ADC12QJ1600[0] INITIALIZATION PROCEDURE

write adc reg | addr : 0x0000 | data : 0x00B0

read adc reg | addr : 0x0270 | data : 0x0001

write adc reg | addr : 0x0058 | data : 0x0083

write adc reg | addr : 0x002B | data : 0x0015

write adc reg | addr : 0x005C | data : 0x0001

write adc reg | addr : 0x003F | data : 0x004A

write adc reg | addr : 0x003D | data : 0x0005

write adc reg | addr : 0x003E | data : 0x0014

write adc reg | addr : 0x005D | data : 0x0041

write adc reg | addr : 0x005C | data : 0x0000

write adc reg | addr : 0x0200 | data : 0x0000

write adc reg | addr : 0x0061 | data : 0x0000

write adc reg | addr : 0x0037 | data : 0x004B

write adc reg | addr : 0x029A | data : 0x000F

write adc reg | addr : 0x029B | data : 0x0004

write adc reg | addr : 0x029C | data : 0x001B

write adc reg | addr : 0x0201 | data : 0x0008

write adc reg | addr : 0x0202 | data : 0x00FF

write adc reg | addr : 0x0204 | data : 0x0003

write adc reg | addr : 0x0062 | data : 0x0005

write adc reg | addr : 0x0065 | data : 0x0001

write adc reg | addr : 0x0057 | data : 0x0080

read adc reg | addr : 0x005E | data : 0x0003

read adc reg | addr : 0x0059 | data : 0x007F

ADC[0] wait for flag : 0x01 in reg_addr : 0x208 data : 0x00 TIMEOUT!

read adc reg | addr : 0x0208 | data : 0x0000

您能帮助我确定我可能会出什么问题吗? 非常感谢您的协助。

感谢您投入宝贵的时间给予大力支持。

此致、

米哈伊尔·瓦西列乌