主题中讨论的其他器件: controlSUITE、 ADS127L01

大家好。 在这里、我面临着通过 ADS127L01EVM (从器件)与 Delfino F2833x 板(主器件)建立 SPI 通信的一些问题、这两者都是 TI 产品。

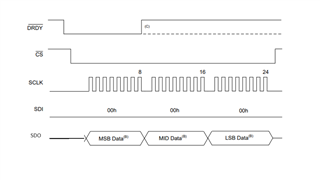

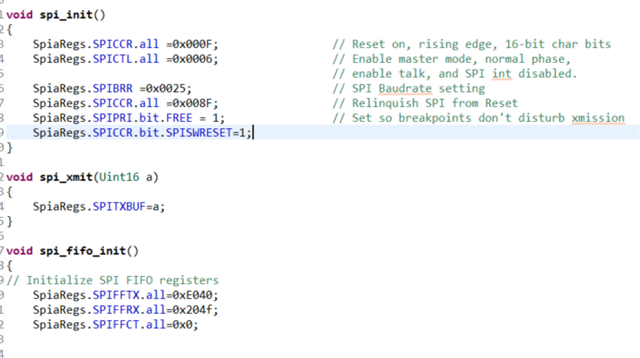

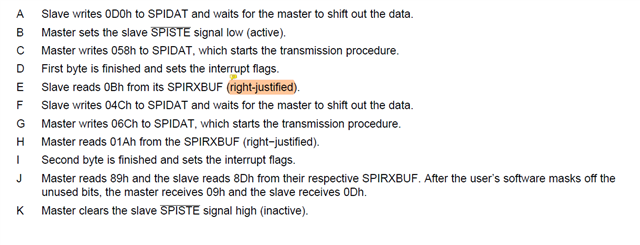

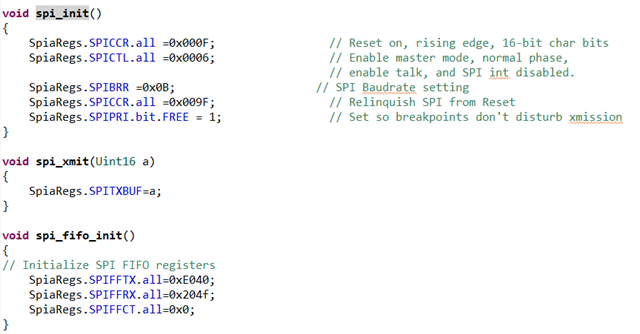

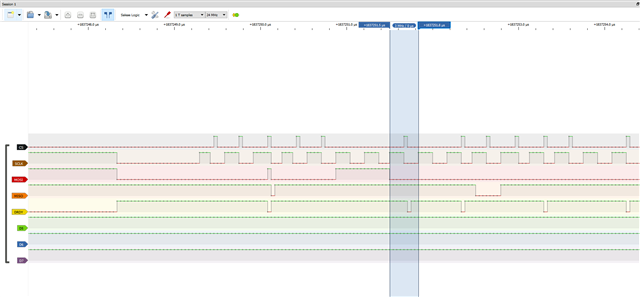

我 已经引用了"controlSUITE"中提供的 SPI_Loopback 代码、并且已经完成了从主器件向从器件发送 SPI 命令的测试、但主器件无法从从从器件接收任何信息。 我使用数字逻辑分析仪监控此 SPI 通信过程。 在这里、我附加了几个 pic 来说明 SPI 协议设置。

以下是一些原本希望能够从 TI 技术团队获得支持的问题:

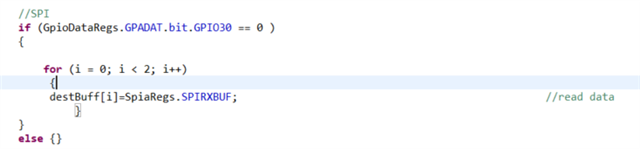

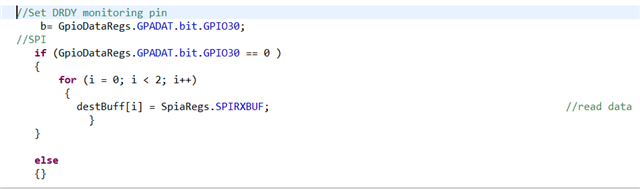

1.对于通过 ADS127L01EVM 设置的 SPI 协议、需要设置一个输入引脚来监控 DRDY 状态、我是否知道下面显示的代码是监控 DRDY 引脚状态的正确方法?

2. CS 引脚会出现一些尖峰,尽管我已经在编码中将 CS 设置为低电平。 此现象是否存在任何问题、它是否会影响 SPI 通信过程? 请参阅下面随附的 pic。

3、根据问题2 pic、SPIBFF I 集为11、但测得的 SPI SCLK 波特率为3M Hz、这不是150m/(SPIBFF+1)= 12.5m Hz。 我是否知道我在 SPI 波特率的设置方面有任何错误。