Other Parts Discussed in Thread: ADS124S08, TMS320F28377D

主题中讨论的其他器件: TMS320F28377D

尊敬的先生:

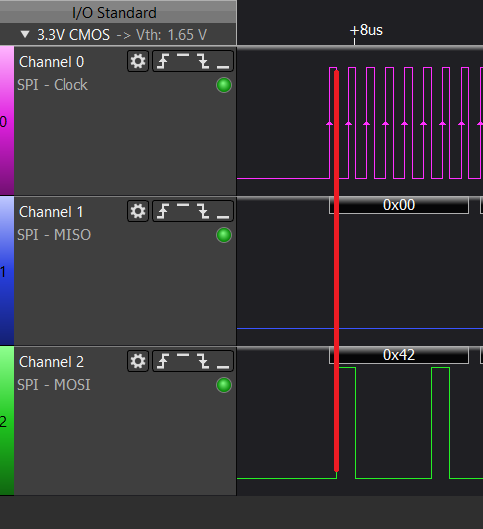

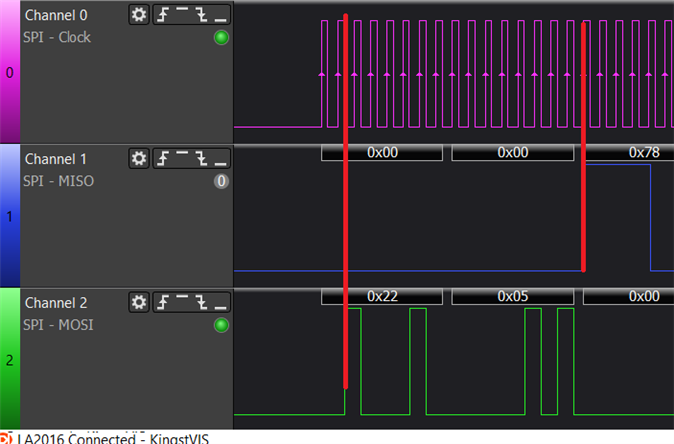

我能够使用 RREG 正确读取默认寄存器(使用 SPI 连接)。 但我在写入和读回一些配置寄存器值时遇到了一个奇怪的问题。 例如:

在我写入时使用 INPMUX 寄存器:

0x12带有 WREG I 回读0x13 (似乎无法将 MUXN 设置为 AIN2)

使用 WREG 为0x16、我回读0x17 (似乎无法将 MUXN 设置为 AIN6)

但有趣的是、它适用于其他设置 (例如 AIN3、AIN4等)

PGA 寄存器也是如此。 当我尝试将 PGA 增益选择设置为2 (0bxxxxx001)时、无法做到、我仍然使用相同的写入和读取方法读取默认值1 (0bxxxxx000)

对于这些观察到的结果、可能的解释是什么。 请参阅随附的逻辑分析仪读数。

非常感谢。

图 1.将命令分别写入寄存器02和03值0x12和0x09。

图 2.读取寄存器02和03时分别显示了值0x13和0x08。