我们设计的机架中有10个 ADS8568板、其中的 FPGA 可读取背板上的 SPI 总线。 进出 ADC 的所有信号上都存在一定数量的振铃、我们 认为测量中偶尔会出现这样的尖峰。 问题是 、ADS8568对数字控制 输入上的振铃有多大的影响? 我们是否需要从所有信号中消除它们以实现可靠运行、或者我们是否可以清除转换并在某个阈值以下发出 spiclk?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好、Winston、

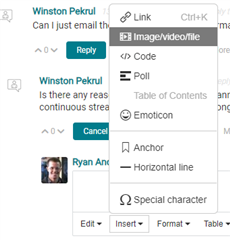

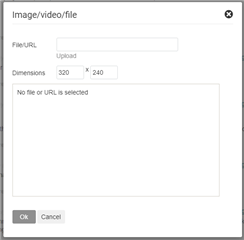

要上传照片、您可以截取屏幕截图并直接粘贴到消息框中、或按照下面所示的菜单选项操作(灰色的"上传"按钮不是很明显、但它会启动文件资源管理器以便您导航和选择保存的图像):

根据您的描述、这听起来像是一个数字数据采集问题、而不是一些模拟输入瞬态。 MSB 与其他位具有不同的传播延迟、并由 FSN 的下降沿("帧同步")启动。 确保在将 SCLK 置于低电平之前至少等待12ns、以捕获 MSB。

使用图1作为参考、您是否可以捕获一帧的界面示波器图像? 我们可以查看 FSN、SCLK、SDO_x 和 BUSY。

此致、

瑞安