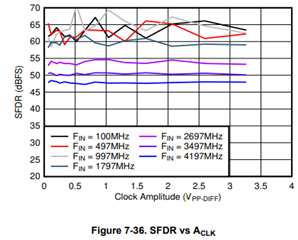

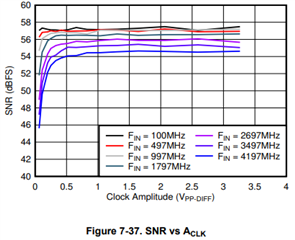

ADC 数据表显示"TI 强烈推荐 CLK±与 DEVCLK_LVPECL_EN 设置为0进行交流耦合、以允许 CLK±自偏置到最佳输入共模电压、从而实现最佳性能。" 因此 建议将 LVDS 作为输入时钟标准。 但是、这只会为我们提供800mV 的 Vpp 输入。 ADC 数据表提供了两个图形、其中显示了随着输入采样时钟振幅的增加、SNR 和 SFDR 性能略有增加:

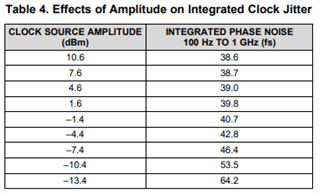

此外、在 TI 的应用手册"TIDU870"中、有一些文档位于 第2.4节抖动导致的 SNR 显示了与输入时钟振幅相关的相位噪声直接性能增加。 请参阅表4:

这引导我们 采用振幅更高的时钟标准、例如交流耦合 LVPECL、但我们很好奇、为什么数据表在性能与输入时钟振幅之间存在这种直接相关性时会特别建议使用交流耦合 LVDS。