请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:DAC3154 主题中讨论的其他器件:DAC3152、

我正在比较 DAC (DAC3152)和(DAC3154)、我想找到哪一种更适合我的设计。

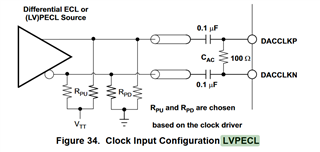

在 DAC3152的数据表中已提到、首选的输入时钟由差分 ECL/PECL

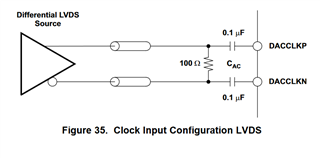

我在 FPGA 的设置中无法获得这个值、因此我要使用 LVDS、这在这里也是一个选项。

这对 DAC3154也起作用吗? 数据表中没有提到这一点、我不确定如何使它像这样工作。 这是一个针对 I/O 可设置的 Xilinx 的 VC707 FPGA 列表。

是否有一种简单的方法可以在没有任何损耗或干扰的情况下实现所需的设置?