Other Parts Discussed in Thread: ADC09QJ1300-Q1, LMK00304

主题中讨论的其他器件: LMK00304

您好、 :工程师 J ü r

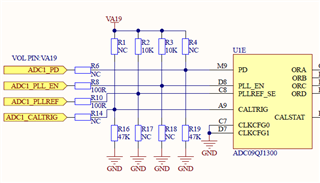

我的 ADC adc09QJ1300-Q1有一些问题。我的电气连接如下所示

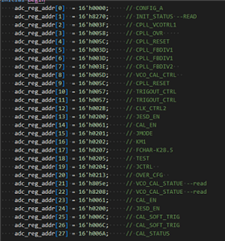

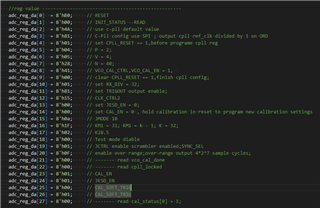

我的寄存器配置的序列地址的相应值如下图所示

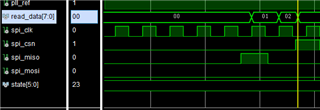

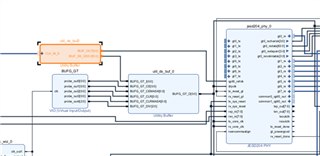

并使用 tirgout 作为 FPGA GTH.fpga 类型的恢复时钟是 ulterslcae xcku060、FPGA 中的 clk 如下图所示

但启动时钟输出不稳定、但 pllref 稳定在50MHz。、并且在配置期间读取 VCO_CAL_STATUS、 并且从寄存器中已知 VCO_CAL_STATUS[7:1]是保留位、位0是 VCO_CAL_DONE 状态位。但是、在实际读取过程中、会读取多个0x20、然后读取一个0x30。 然而、采集触发时钟仍然不稳定。 您要问的问题是什么?