大家好、我正在阅读 LM98640QML-SP 的数据表、我发现§8.2.1有点令人困惑:这里的名称是"采样/保持模式"、但图29说明中提到的是"典型的 CDS 模式应用图"。 那么、图29中显示的到底是什么配置?

为了我的特殊用途、我想使用 LM98640QML-SP 来测量检测器的四个1.5V 共模/差分输出、因此我会使用两个 LM98640QML-SP、并为每个差分输出同时使用 OS1/2+和 OS1/2-输入。 您能解释一下在我的特定案例中、我应该遵循什么应用图表?

谢谢你。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

大家好、我正在阅读 LM98640QML-SP 的数据表、我发现§8.2.1有点令人困惑:这里的名称是"采样/保持模式"、但图29说明中提到的是"典型的 CDS 模式应用图"。 那么、图29中显示的到底是什么配置?

为了我的特殊用途、我想使用 LM98640QML-SP 来测量检测器的四个1.5V 共模/差分输出、因此我会使用两个 LM98640QML-SP、并为每个差分输出同时使用 OS1/2+和 OS1/2-输入。 您能解释一下在我的特定案例中、我应该遵循什么应用图表?

谢谢你。

尊敬的 Carlos:

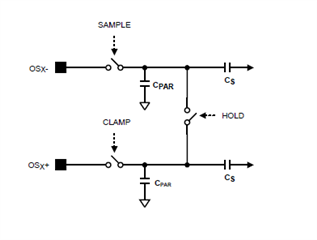

数据表中的图29确实跟在采样保持模式之后、但是其中基准为 VCLP。 因此、它们短接至 VCLP。

该器件 构想为来自图像传感器的单端输入。 对于差分输入用例、您必须微调寄存器设置。 我强烈建议您在继续进行最终的电路板设计之前在 EVM 上尝试该操作。

由于您的输入是差分和1.5V 共模、您 可以 使用采样保持模式。 您 可以将输入直流耦合到 OSx+和 OSx-引脚(例如、没有输入耦合电容器)。 OSx+不应短接至 VCLP、也不应具有接地的旁路电容。

OSx-将记录在采样时钟上、OSx+将记录在钳位时钟上(CLPIN 门控启用、CLPIN 始终为高电平)。 您必须调整采样时钟和钳制时钟以记录正确相位的像素电压。

谢谢。

K·N