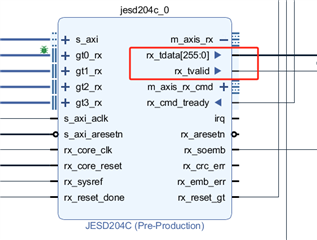

大家好、我使用了 Xilinx FPGA 和 ADC09QJ1300来完成 JESD204C 的设计。 目前、我可以在 Vivado 中看到 Xilinx 的 JESD204C 的 IP 输出数据。

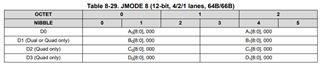

如图所示、我使用 JMODE 8、而 IP 的输出端口是一个256位的数据。 据我所知、在该256位中、每个通道占用64位。

但我仍然不知道如何在每个通道的64位内提取样本。 我查看了数据手册的[8.4.2.1 JESD204C Transport Layer Data Formats]部分、但仍不了解如何处理数据。

我希望获得一个明确的指示、例如哪些位在64位数据中是采样信息。

我已经阅读了很多天,但我仍然不理解它,所以我来寻求帮助,非常感谢您的帮助