您好!

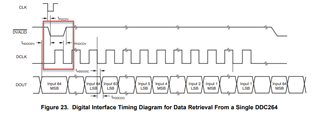

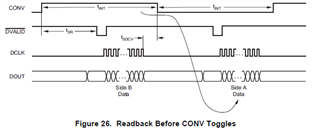

我有一个问题要请教那些有 DDC264EVM 评估板及其软件经验的人。 我尝试在评估板中使用四个 DDC264来设置 FPGA 配置寄存器、以便积分时间为1ms。 基本而言、我希望在 CONV 信号切换之前执行数据检索、如下图所示:

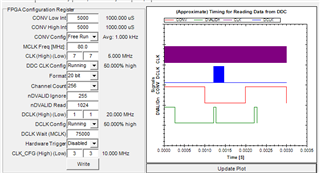

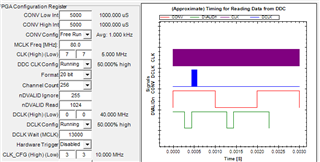

我设置了20MHz DCLK、5 MHz CLK 和 CONV 5000 CLK 周期 (1000ms)、但是问题是、当我设置了更大的 DCLKWait 值以将 DCLK 脉冲置于 CONV 低电平有效状态时、DVALID 脉冲变得太宽。 如果有人知道我在做什么错,或者已经处理了很长的整合时间,并具有适当的参数,我会很高兴。