Other Parts Discussed in Thread: ADS4249

您好!

我的客户正在测试他们使用 ADS4249设计的电路板。

他们说在 ADS4249的 RF IN 端口上可以观察到245.76MHz 的基准时钟。

在哪些情况下会出现这种症状?

是否可以通过某种方法降低射频输入端口的参考时钟噪声级别?

谢谢你。

JH

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

尊敬的 Rob:

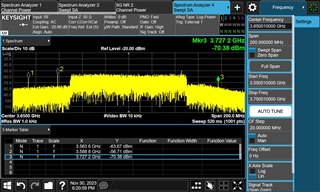

由于客户使用的是245.76 MHz 的采样率、上述 ADC 输出数据在 DC 中将具有245.76 MHz。

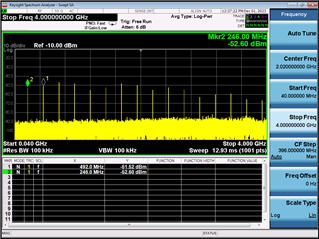

下面是 SA 捕获的图像、客户在中的"射频块"和"ADC 射频"之间进行了检查。

-参考时钟信号(246.76MHz) x N 信号输出来自 ADC 输入

-当该 CLK 信号与系统的 LO 信号相结合时,在输出频带附近产生一个杂散信号,导致了一个滤波器无法消除的问题。

1820MHz LTE 3650MHz 5G NR

请提供有关如何解决此问题的建议。

谢谢。

JH

您好、JH:

原理图看起来没有问题。 对于客户所关心的问题、我仍然感到困惑。

您将再次在模拟输入端使用频谱分析仪探头看到时钟频率杂散。

这是非缓冲 ADC 内部采样架构固有的特性。

在从 ADC 捕获的数据中、应不存在时钟伪波...我在上面提供的 FFT 中看不到该杂散。

以下是描述此行为的应用手册:

www.analogue.com/.../an-742.pdf

此致、

Rob