请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:AFE5818EVM 您好!

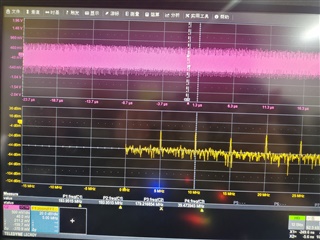

一位客户使用带 FPGA 的 AFE5818EVM 写入命令来测试 SPI 的数据输出、采样率为40ms/s、输出 DCLK、FCLK 和数据正常。 但当他用信号发生器输出5MHz、5Vpp 正弦波到通道1时、DCLK 是不稳定的、它大约在200MHz 到280Mhz 之间跳跃、他进行了 FFT 分析、结果如下、我们可以发现除了5MHz 外有很多多频峰值。

如果 WRITE 命令不正确、请帮助分析导致此问题的原因。

此致

凯林