请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:ADS7029-Q1 DS 中未包含 SPI 时序参数。 它们将何时记录在数据表中?

SPI 时钟上升/下降时间最小/最大输入要求是什么?

SPI 数据输入上升/下降时间要求是什么?

SPI 数据输出上升/下降时间 规格是什么?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

DS 中未包含 SPI 时序参数。 它们将何时记录在数据表中?

SPI 时钟上升/下降时间最小/最大输入要求是什么?

SPI 数据输入上升/下降时间要求是什么?

SPI 数据输出上升/下降时间 规格是什么?

Andy、您好!

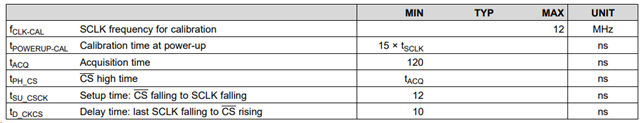

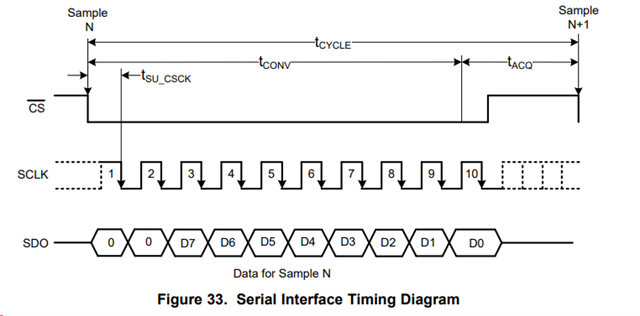

感谢您的提问。 我认为您要查找的信息位于 DS 的第6.6节(时序要求) 8.3.4节(串行接口)和8.4节(器件功能模式)中。 下面是一些时序参数的屏幕截图:

SPI 传输帧由 CS 信号设置。 帧从 CS 下降沿开始、到 CS 上升沿结束。 CS 下降沿和第一个 SCLK 下降沿之间必须有最小延时 t_SU_CSCK (12ns)。 数据在 SDO 引脚上移动。 转换数据的前两位设为0、后接8位。 该器件只有一个 SDO 引脚、无 SDI 引脚。 串行接口可用于将 ADC 转换结果传输到外部主机。

如果您有任何其他问题、敬请告知。

此致、

评估