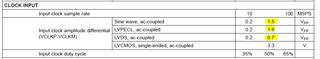

主题中讨论的其他器件:AFE5818、

尊敬的先生或女士:

我正在尝试确定采样 CLK 需要远端还是近端端。

根据评估板、端接似乎在变压器侧。 这表明引脚59、58上有一些低阻抗输入。

确定差分信号的波阻抗。 是否布线的评估板上的 PCB 迹线?

感谢您的全力帮助。

此致、

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好!

我代表我的同事答复,因为他目前正在休假。

IBIS 模型在这里可用、但我不看到时钟输入的模型

https://www.ti.com/product/ADS5263#design-development

我们需要等到我的同事下周度假回来了解更多细节。

谢谢!

此致、

沙比尔

尊敬的 Gruffalo:

遗憾的是、IBIS 模型不适用于 CLKP 和 CLKM 引脚。

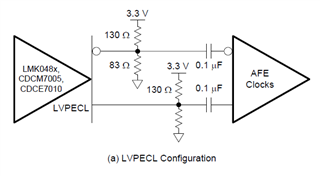

CLKP 和 CLKM 不是低阻抗引脚。 实际上、它们为高阻抗、因为这些引脚将连接到时钟缓冲器。 这些时钟线 在 PCB 上应按照100欧姆差分电阻布线、并在 ADC 附近端接100欧姆差分电阻。

时钟缓冲器不是传统的 LVPECL 缓冲器、因此请对时钟输入进行交流耦合。 根据数据表、当检测到时钟时、可检测到200mVpp 及以上的差动摆幅。

下面的电路来自 AFE5818。 您可以遵循类似的电路为 ADS5263提供 LVPECL 时钟。 将130欧姆和80欧姆对靠近 ADC 放置。 它们实际上充当100欧姆差分电阻。

谢谢。

卡尔蒂克