团队、

我们将运行 TSW1400。 我们发现 FCLK 出现在 Samtec 连接器上、但其波形不良。 USER_LED3有时 会亮起和熄灭(表示 FPGA PLL1已锁定到来自端口0的 ADC 输入时钟)

这让我觉得 TSW1400需要良好的时钟。 我们的 FCLK 是40MSPS、DCLK 是240MSPS。我认为 TSW1400使用 FCLK 来运行内部 PLL。 只是想再次确认。

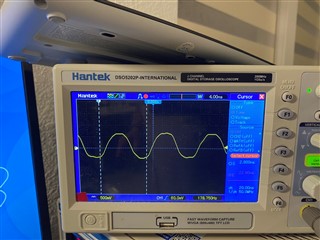

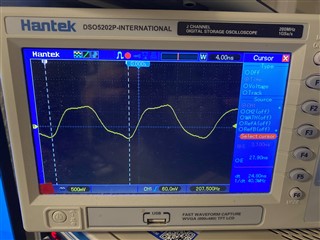

测量的 FCLK 如下所示。 40MHz 来自我们的系统板、50MHz 来自 TI EVM。 TI AFE/ADC EVM 信号当然更好。 我们的布线较长、之间有多个连接器。 有什么想法吗?

我将在时钟电路上工作以减慢它,看看.

非常感谢!

晓辰