主题中讨论的其他器件:LMK04828

您好:

我只是 想确保 ADC12DJ5200的频率和 SYSREF 的确切值是多少? 如下图:

我设置板载 Fs :2000Msps . 模式:JMOD31。

JESD204 通道速率是否为6.6Gbps?

是 FPGA_CLK 100MHz 吗?

如何计算 ADC 和 FPGA 的 SYSREF?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好:

我只是 想确保 ADC12DJ5200的频率和 SYSREF 的确切值是多少? 如下图:

我设置板载 Fs :2000Msps . 模式:JMOD31。

JESD204 通道速率是否为6.6Gbps?

是 FPGA_CLK 100MHz 吗?

如何计算 ADC 和 FPGA 的 SYSREF?

您好!

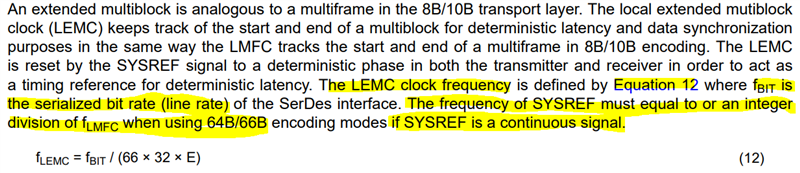

如果 sysref 是连续的、那么它必须相等或为 LMFC 频率的整数比、这可以使用公式

f_lmfc = f_bit /(10*F*K)有关详细信息、请查阅第84页的数据表第7.3.9.4.2节。

ADC 时钟将是您在 GUI 中设置的任何值。在本例中、2000 MHz 看起来是一样的、sysref 将与 LMK04828的输出相同。 ADC 时钟和 FPGA 时钟并不相同。

此致!

埃里克

尊敬的 CIOU:

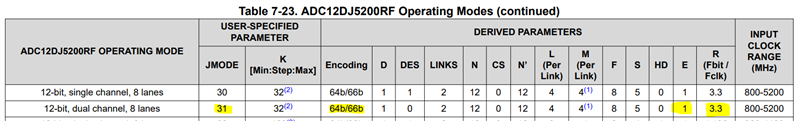

该计算可在数据表中找到、请参阅以下文档。

使用 R (f_clk/f_bit)、可通过 fs*R 计算 SerDes 速率。 在 JMODE31中、R=3.3、E=1。 这将产生线速率(f_bit)= 2e9 * 3.3 = 6.6Gbps。

允许的最大周期 SYSREF 频率为 f_LEMC。 SYSREF 可以是该值的任意整数倍。 否则、SYSREF 将不会在正确的边界时间出现、从而导致错误。

F_LEMC=6.6e9/(66*32*1)= 3.125MHz。 就100MHz 的除法而言、正如 Eric 先前提到的、该分频器值为32。

谢谢,Chase