Other Parts Discussed in Thread: DAC3283, CDCE62005

主题中讨论的其他器件:DAC3283、 CDCE62005

我们使用 Iwave 系统 FPGA 连接了 DAC3283。 我们能够使用以下频率配置 CDCE:

dac clk : 614 MHz

FIFO OSTR 时钟: 19.2 MHz

FPGA clk:76.8MHz

插值: 4倍

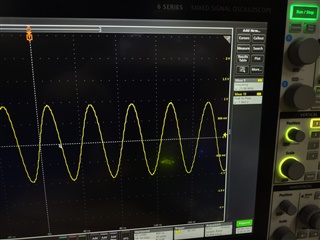

我们使用 FPGA 内部的 FPGA clk 生成方波信号并将其发送到 DAC。

Data clk : 307.2 MHz

帧时钟:19.2MHz

方波信号频率:38.4MHz

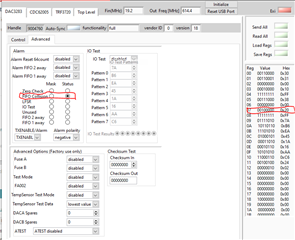

在执行 DAC3283用户指南的第4.1节中提到的必要更改后、我们尝试在 J3连接器上查看 DAC 输出。

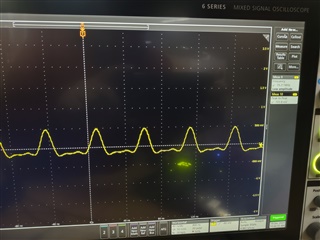

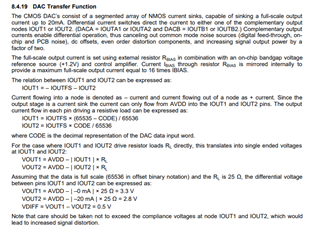

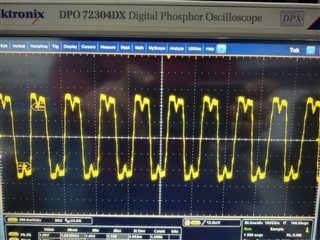

我们已使用示波器进行检查、确认上述所有时钟和数据都到达 DAC 引脚、但没有来自 J3的输出。 DAC IC 上的 IOUT 引脚始终显示恒定的3.3V、即使来自 FPGA 的数据不存在也是如此。

此外还随附了配置文件、用于配置 DAC3283和 CDCE62005。