请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

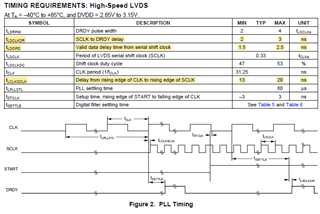

器件型号:ADS1675 我正在设计16 x ADS1675、它可以在同步模式下工作。 当所有 ADC 在相同的电压、3.0V +/-1%上运行时, CLK 到 SCLK 的延迟是什么,例如,TLCLKSCLK 在40°C 到70°C 之间。 随附是数据表中的相关图2时序图;请注意、数据表给出了电压和温度以及过程的延迟。 在这里、我想问的是、仅凭流程、我可以预期 PLL 时序会有什么变化。