需要有关 DAC37J82配置的帮助、模拟输出引脚无输出!!

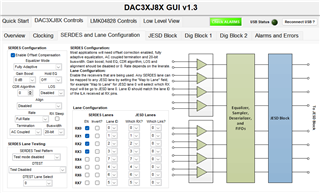

我们使用的是 采用 JESD204B 协议的 DAC37J82、连接到 FPGA SOM - Xillinx Zynq Ultrascale+ MPSoC ZU19EG、使用 LMK04828B 作为时钟分配器、为 DAC 和 FPGA 提供 REF CLK 和 Sysref 时钟。

使用 DAC 的 CH_A 和 CH_C、

附加 DAC 配置和 DAC 原理图。

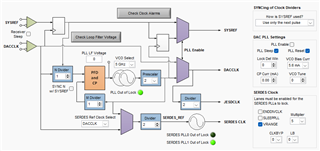

时钟分配器–LMK04828B

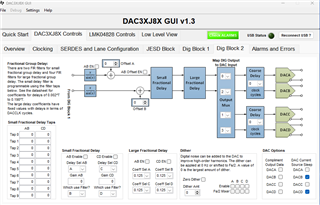

DAC 数据输入速率- 250MSPS , LMFS=4211, 插值 = 1,

DAC jesd204b 配置–4211、K=20、F=1、 子类=1

DAC 时钟250MHz \ Sysref 6.25MHz

路径设置:config34,(1B27)

采样0 ->路径 A -> DAC A

样本1 ->路径 b -> DAC C

睡眠模式下的 DAC B 和 DAC D

在为 Sysref 加载配置并触发 LMK 后、 DAC Alarm 寄存器似乎正常、我们在示波器中看到 SYNC~ Go 下降

SYSREF 警报正常(DAC 寄存器警报0x6C)、线路对齐正常(DAC 寄存器警报0x64、0x65、0x66、0x67)均读取0x0000

但在 模拟 扩散器上仍然没有输出。 引脚 IOUTAP/IOUTAN ??? --> 为什么????

同样、在 DIIFR 下也无输出。 IOUTCP/IOUTCN ???