Other Parts Discussed in Thread: TRF1208, ADS54J64, LMH5401, THS4541

主题中讨论的其他器件: LMH5401、TRF1208、 THS4541

您好!

我目前正在设计 用于粒子加速器仪表应用的宽带接收器(频率范围从1 MHz 到几百 MHz)。 要将我们的信号数字化、我们需要使用 ADS54J64、以实现其高采样率和 JESD 功能。

我们计划使用 ADL5536放大器(20dB 增益块、~+20dBm 的 O1dB)在 ADC 之前增强我们的信号。 不过、通过查看 ADS54J64的数据表、我们可以看到一个潜在的问题、即如果 出现意外的输入信号条件、该特定的放大器可能会输出超过最大电压摆幅的信号。 在继续设计过程之前、我希望确保我对这个评分的理解是正确的。

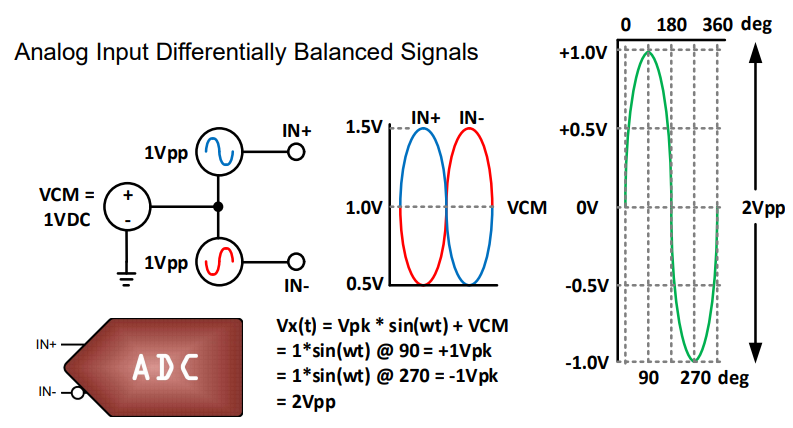

数据表第5页分别说明了-0.3V 和+2.1V "施加到输入引脚的电压"的绝对最小值和最大值。 不过、我还知道 ADC 通道在内部偏置为1.3V 的输入共模电压(Vcm)。这是否意味着最大容许电压摆幅为-1.6V 至+0.8V? 或者、INxP 和 INxM 上的偏置是否已经变化、这样的话、一个-2.1V 至+2.1V 的摆幅是可耐受的? 在回答这些问题时、我所了解的是如何解读最大"施加到输入引脚的电压"和 ADC 的 VCM。

我们需要利用放大器的饱和输出功率、使接收器在本质上无法过驱 ADC。 +20dBm (假设 O1dB 接近饱和输出功率)可转换为3.1的峰值电压、该电压在 ADC 之前的1:1平衡-非平衡变压器之后变为-1.58V 和+1.58V。 这会损坏 ADC 吗? 如果需要、我们可以采取什么措施来缓解这种情况? 我们进行的测量是差分测量、这意味着尽可能减小接收器通道之间的差异至关重要。 如果可能、我们不想更改放大器。

感谢您的帮助。 我期待您的答复。

此致!

亚当