主题中讨论的其他器件: TLV9102、 REF6050、 REF5050、 OPA320、 ADS8860

尊敬的技术支持团队:

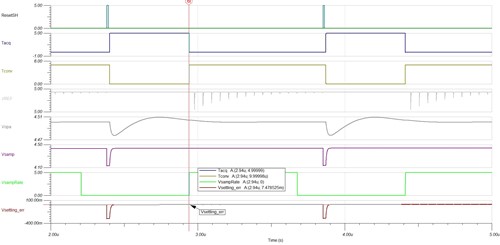

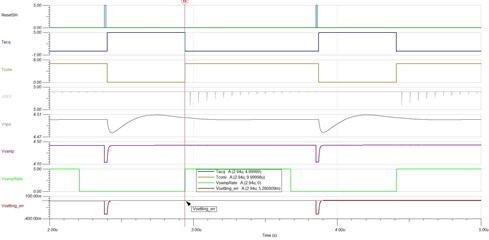

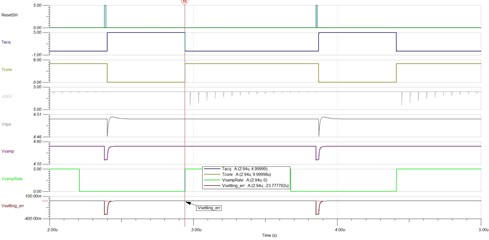

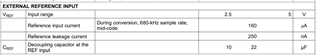

ADS8862数据表显示电荷反冲滤波器、RFLT≦22Ω 和 CFLT≧590 pF (图62. 电荷反冲滤波器)、但我的配置只是采用 TLV9102的 ADC 驱动器的 RC 滤波器。

我针对 TLV9102 (缓冲器)发布、RC 滤波器的2.2kΩ、C=2700pF、并附带文件(方框图)

我正在确认后续 E2E 上的相位裕度和稳定性。

附加文件

e2e.ti.com/.../TLV9102_5F00_ADC.pdf

我想确认、即使图表62之间的配置和常数不同、ADS8862是否没有问题。 电荷反冲滤波器和电路板的 RC 滤波器。

另外、如果您对简单 RC 滤波器有任何想法或建议的常数、请告诉我。

此致、

TTD